# 000 001 002 003 004 005 AMSBENCH: A COMPREHENSIVE BENCHMARK FOR 006 EVALUATING MLLM CAPABILITIES IN AMS CIRCUITS 007 008 009

010 **Anonymous authors**

011 Paper under double-blind review

012

013

014

015

016

017

018

019

020

021

022

023

024

025

026

027

028

## ABSTRACT

011 Analog/Mixed-Signal (AMS) circuits play a critical role in the integrated circuit

012 (IC) industry. However, automating Analog/Mixed-Signal (AMS) circuit design has

013 remained a longstanding challenge due to its difficulty and complexity. Although

014 recent advances in Multi-modal Large Language Models (MLLMs) offer promising

015 potential for supporting AMS circuit analysis and design, current research typically

016 evaluates MLLMs on isolated tasks within the domain, lacking a comprehensive

017 benchmark that systematically assesses model capabilities across diverse AMS-

018 related challenges. To address this gap, we introduce AMSbench, a benchmark

019 suite designed to evaluate MLLM performance across critical tasks including circuit

020 schematic perception, circuit analysis, and circuit design. AMSbench comprises

021 approximately 8000 test questions spanning multiple difficulty levels and assesses

022 eight prominent models, encompassing both open-source and proprietary solutions

023 such as Qwen 2.5-VL and Gemini 2.5 Pro. Our evaluation highlights significant

024 limitations in current MLLMs, particularly in complex multi-modal reasoning

025 and sophisticated circuit design tasks. These results underscore the necessity of

026 advancing MLLMs' understanding and effective application of circuit-specific

027 knowledge, thereby narrowing the existing performance gap relative to human

028 expertise and moving toward fully automated AMS circuit design workflows. Our

029 data is released at this URL.

030

031

032

033

034

035

036

037

038

039

040

041

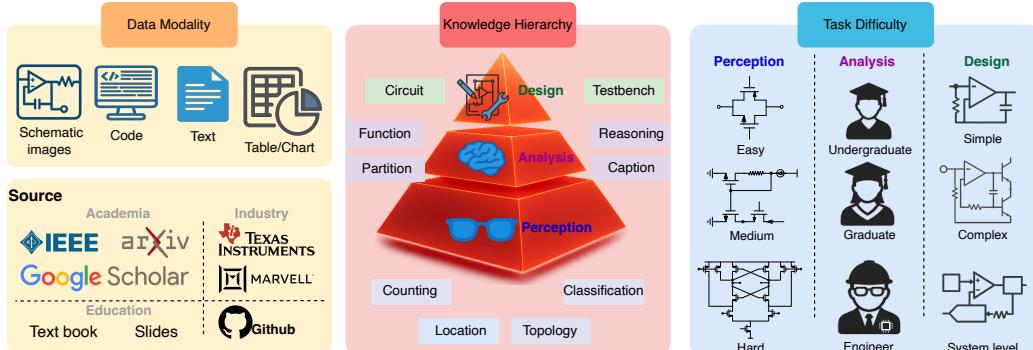

042 Figure 1: **Overview of AMSbench.** AMSbench includes multimodal question-answer pairs collected from both

043 academia and industry. The tasks are divided into schematic perception, circuit analysis, and circuit design.

044

045

## 046 1 INTRODUCTION 047

048 The rapid advancement of large language models (LLMs) and multimodal large language models

049 (MLLMs) has led to significant breakthroughs across diverse domains, including autonomous driving

050 (Cui et al., 2024), scientific research (Hao et al., 2025; Yue et al., 2024), mathematics (Zhang

051 et al., 2024; Lu et al., 2023; Yang et al., 2024b), and programming (Zhong & Wang, 2024). In the

052 domain of Electronic Design Automation (EDA), these models have shown promise, particularly

053 in the automated design of digital circuits (Bhandari et al., 2025). On the contrary, automating

analog/mixed-signal (AMS) circuit design has been a longstanding challenge for its reliance on

054 human experience. Today’s AI-driven automatic AMS design still faces considerable challenges due

055 to the scarcity of high-quality data and the intrinsic complexity of multi-modal data. As a result, the

056 exploration and application of LLMs in AMS circuit design remain limited and exhibit relatively poor

057 performance (Gao et al., 2025; Lai et al., 2025; Chen et al., 2024). Furthermore, current applications

058 focus on verbal information, while AMS circuits rely on other modalities as well, such as schematics,

059 plots, and charts.

060 A primary obstacle lies in the limited capability of existing MLLMs to accurately interpret circuit

061 schematics. Unlike netlists, schematics convey richer and more nuanced structural information

062 beyond abstract connectivity. Recent work (Tao et al., 2024; Bhandari et al., 2025) has recognized

063 this limitation and introduced tools capable of automatically converting schematics into netlists,

064 thereby enabling the creation of large-scale, high-quality datasets suitable for training models. Recent

065 advances in the visual capabilities of MLLMs (e.g., GPT-4o (Hurst et al., 2024) and Qwen2.5 (Yang

066 et al., 2024a)) have significantly improved schematic recognition accuracy, laying a solid foundation

067 for the automated analysis and design of AMS circuits. Despite these advancements, current applica-

068 tions often focus on isolated tasks—such as netlist generation (Lai et al., 2025; Liu et al., 2024) and

069 error identification (Chaudhuri et al., 2025)—while lacking comprehensive evaluation frameworks.

070 In particular, there has been little systematic in-

071 vestigation into the following three fundamental

072 questions:

- 073 1. How accurately can models recognize and

074 interpret AMS circuit schematics?

- 075 2. What is the upper bound of domain-specific

076 knowledge that models can attain in AMS circuit

077 analysis and design?

- 078 3. To what degree are models capable of sup-

079 porting the automation of AMS circuit design?

081 To address these questions and bridge the ex-

082 isting research gaps, we propose AMSbench, a

083 comprehensive benchmark designed to evaluate

084 the capabilities of advanced models in the con-

085 text of AMS circuit design. AMSbench assesses

086 model performance across three key dimensions:

**perception, analysis, and design.**

088 In the perception task, the objective is to eval-

089 uate how accurately MLLMs can generate netlists

090 directly from circuit schematics, reflecting their schematic recognition capabilities. This is a non-

091 trivial challenge due to the large number of components and their intricate interconnections. We

092 further decompose this task into sub-tasks such as component counting, component classification, and

093 interconnect recognition, culminating in the primary goal of accurate netlist generation. The analysis

094 task examines the models’ understanding of circuit-related images, ability to identify critical building

095 blocks, and comprehension of trade-offs among performance metrics—key aspects in AMS circuit

096 design and verification. Finally, the design task investigates whether models can synthesize circuits

097 that satisfy given specifications. We also evaluate their ability to generate appropriate testbenches to

098 assess circuit performance across multiple criteria.

099 To the best of our knowledge, AMSbench is the first holistic benchmark that systematically evaluates

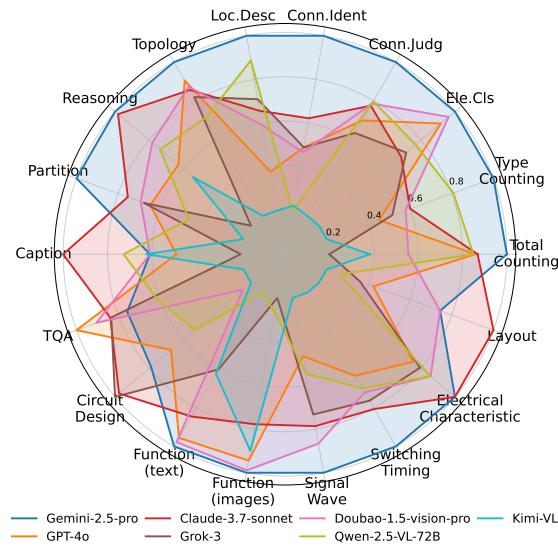

100 the performance of advanced models in AMS circuits. The overall benchmarking results of state-

101 of-the-art models using AMSbench are illustrated in Fig. 2. Our contributions are summarized as

102 follows:

- 105 • We construct **AMSBench**, a large-scale, high-quality multimodal benchmark designed to

106 rigorously evaluate the perception, analysis, and design capabilities of MLLMs in the AMS

107 circuit domain. AMSbench consists of three major components: AMS-Perception (6k),

AMS-Analysis (2k), and AMS-Design (68).

Figure 2: Comparison of top MLLMs on 18 sub-tasks(w/o DeepSeek-R1 on VQA tasks, which lacks visual processing capability)

- 108 • We conduct a comprehensive evaluation of both open-source and proprietary models on

109 AMSbench, providing detailed comparisons and performance insights across all tasks.

110 Furthermore, we present in-depth analyses highlighting the key challenges that must be ad-

111 dressed to enhance the applicability of (M)LLMs in the AMS circuit domain, and we further

112 discuss several potential solutions and research directions to overcome these challenges.

- 113 • We release the AMSbench dataset at the provided URL, fostering transparency and repro-

114 ducibility in this emerging research area.

116 Table 1: Comparison between existing AMS datasets and benchmarks. *Task* includes three categories: P

117 (Perception), A (Analysis), and D (Design). Q&A stands for Question and Answer.

| 119 <b>Dataset/Benchmark</b>           | 120 <b>Modality</b> | 121 <b>Task</b>         | 122 <b>Size</b>      | 123 <b>Label Type</b> | 124 <b>Difficulty Level</b>        |

|----------------------------------------|---------------------|-------------------------|----------------------|-----------------------|------------------------------------|

| 120 AMSnet (Tao et al., 2024)          | 121 Image-only      | 122 P                   | 123 1K               | 124 Netlist           | 125 ✗                              |

| 121 Masala-CHI (Bhandari et al., 2025) | 122 Text & Image    | 123 P                   | 124 6K               | 125 Netlist, Caption  | 126 ✗                              |

| 122 AnalogGenie (Gao et al., 2025)     | 123 Text & Image    | 124 D                   | 125 3K               | 126 Netilsit          | 127 ✗                              |

| 123 Analogcoder (Lai et al., 2025)     | 124 Text-only       | 125 D                   | 126 24               | 127 Netlist           | 128 ✓                              |

| 124 MMCircuitEval (Zhao et al., 2025)  | 125 Text & Image    | 126 P&A&D               | 127 3k               | 128 Q & A             | 129 ✓                              |

| <b>AMSbench(Ours)</b>                  |                     | <b>Text &amp; Image</b> | <b>P&amp;A&amp;D</b> | <b>8K</b>             | <b>Netlist, Caption, Q &amp; A</b> |

## 127 2 RELATED WORK

### 128 2.1 LLM FOR CIRCUIT DESIGN

131 LLMs have demonstrated remarkable potential in the field of EDA, excelling in tasks related to

132 system-level design (Yan et al., 2023), RTL (Blocklove et al., 2023; Fu et al., 2023), synthesis

133 and physical design of digital circuits. This success is primarily due to the modular nature of

134 digital circuit descriptions, which resemble software languages. However, AMS circuit designs,

135 with their transistor-level descriptions, pose a significantly greater challenge for LLMs in terms

136 of accurate understanding and description. Some exploratory work has been undertaken in AMS

137 circuit design (Pan et al., 2025; Fang et al., 2025). Artisan (Chen et al., 2024) develops a LLM that

138 automatically generates operational amplifiers by combining advanced prompt engineering techniques

139 like Supervised Fine-Tuning (SFT) and Tree of Thought. Analogcoder (Lai et al., 2025) proposes

140 using LLMs with predefined sub-circuit libraries to achieve an iterative design and optimization flow.

141 AnalogGenie (Gao et al., 2025) converts circuit topologies into Eulerian circuit representations and

142 uses SFT for synthesizing circuits based on the design requirements. To ensure that the generated

143 circuits can meet specifications, AnalogGenie applies Reinforcement Learning with Human Feedback

144 (RLHF) (Ouyang et al., 2022) as a post-training technique. ADO-LLM (Yin et al., 2024) combines

145 LLMs with Bayesian optimization to generate higher-quality candidate design samples, enhancing

146 efficiency in the transistor sizing process. Layout Copilot uses multiple intelligent agents to improve

147 the efficiency and performance of automated layout generation. AMSnet-KG (Shi et al., 2024)

148 employs a knowledge graph-based RAG (Retrieval-Augmented Generation) approach, based on

149 a large-scale, pre-constructed circuit database, to select and generate circuit topologies that meet

150 specifications. However, it is worth noting that these studies mainly focus on purely language-based

151 LLMs, while circuit design often relies heavily on schematic diagrams. Both Masala-CHAI (Bhandari

152 et al., 2025) and AMSnet (Tao et al., 2024) have pointed out that existing MLLMs still lack the

153 capability to effectively recognize circuit schematics.

### 154 2.2 BENCHMARKING FOR EDA

155 The academic infrastructure for LLM research in EDA has made significant progress. Abundant

156 available benchmarks and datasets have facilitated effective development of LLMs in EDA. Verilo-

157 gEval (Liu et al., 2023) and RTLLM (Lu et al., 2024) introduce benchmarks for evaluating RTL code

158 generation. However, these benchmarks focus primarily on digital circuits. Due to the complexity

159 and irregularity of analog circuits, AMS circuit design is highly experience-driven, making it difficult

160 to establish fair evaluation methods. Hence, benchmarks in the analog circuit domain remain scarce.

161 We summarize the existing datasets and benchmarks for AMS circuits in Table 1. Analogcoder (Lai

162 et al., 2025) proposes a benchmark to evaluate LLMs in AMS circuit design, categorizing circuits

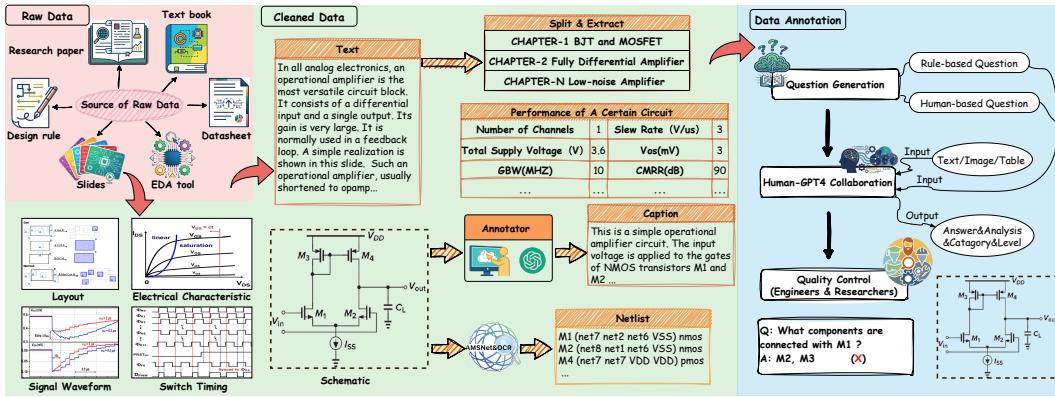

Figure 3: Pipeline of AMSbench construction process.

into three levels: easy, medium, and hard. However, it is limited to the main circuits and did not touch any testbench. Currently, benchmarks in the AMS circuit and EDA domains are limited to verbal questions. However, AMS circuit design is naturally multi-modal, as designers are required to recognize, understand, and reason about circuit schematics.

### 3 AMSBENCH CONSTRUCTION

#### 3.1 DATA COLLECTION AND CURATION

To cover a wide range of knowledge and typical question types in the AMS circuit domain, we gather a diverse collection of research papers, textbooks (Razavi, 2005; Gray et al., 2009; Allen & Holberg, 2011; Sansen, 2007), commercial circuit datasheets and EDA tool. We convert all documents from PDF to Markdown format using MinerU (Wang et al., 2024), enabling efficient extraction of embedded visual elements such as circuit schematics. For schematic-to-netlist translation, we utilize AMSnet (Tao et al., 2024) and OCR, which allows us to accurately recover component-level connectivity and circuit topology. To enrich the dataset with semantic information, we use a combination of manual annotations from field experts and outputs from state-of-the-art MLLMs (Hurst et al., 2024; Yang et al., 2024a). We then apply carefully crafted prompt engineering and filter strategies to generate detailed schematic captions. This process yields high-quality pairs of <circuit schematic, caption>. For textbook-derived data, we organize content according to the logical structure and chapter alignment of each source. For datasheet content, we extract structured performance specifications associated with each circuit.

Based on the extracted information, we build a question–answer dataset, where questions are generated through rules and manual design, and answers are obtained from both human experts and LLMs. We adopted a multi-stage data quality control process, relying on professional circuit engineers as well as doctoral and master’s students in circuit-related fields to filter and refine the generated data, thereby assisting in the construction and quality assurance of AMSbench, as illustrated in Fig. 4.

#### 3.2 EVALUATION

The goal of AMSbench is to thoroughly evaluate MLLMs on the potential applications and tasks in the AMS circuit domain, as shown in Fig. 1. For the design of specific problems, we develop a multi-dimensional evaluation framework that includes **perception**, **analysis**, and **design**. This framework addresses the potential uses of MLLMs in assisting users with interpreting and designing circuit schematics, both automatically and semi-automatically. Considering the complex data modalities and diversity within the AMS circuit domain, the tasks encompass Visual Question Answering (VQA) and Textual Question Answering (TQA). These include multiple-choice questions, computational problems, and open-ended generative questions. We systematically construct questions for each task at multiple levels to accommodate various difficulties and circuit types.

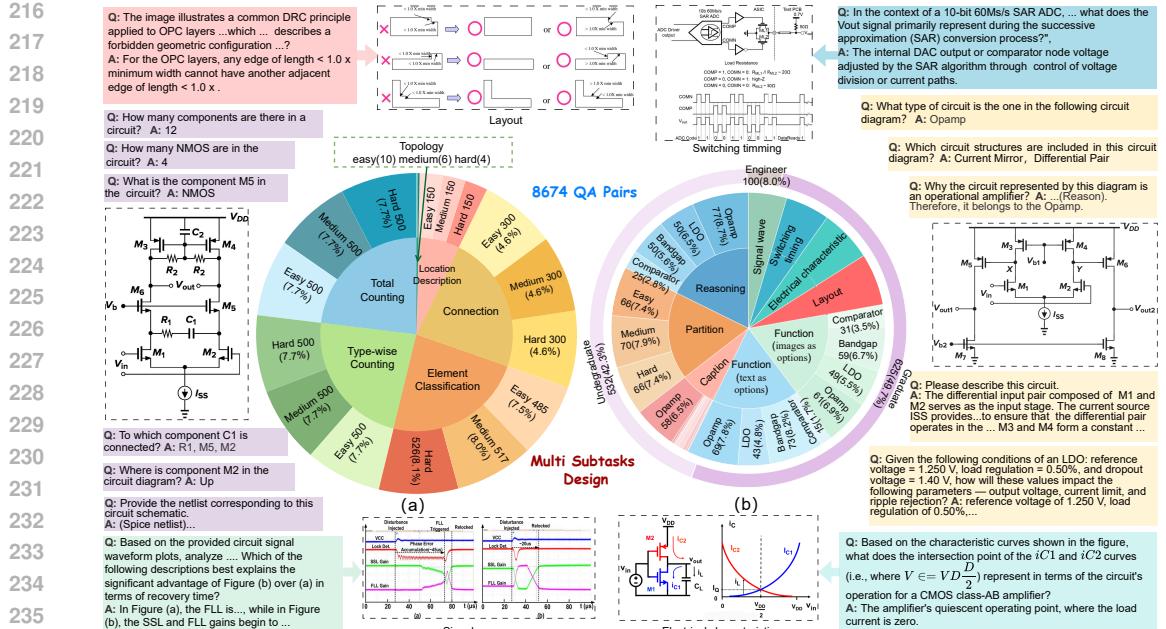

Figure 4: Statistics and examples of AMSBench. Purple regions indicate perception task examples, whereas the others correspond to analysis task examples. (a) Distribution of perception task data. (b) Distribution of analysis task data.

**Evaluation Dimensions** For the **perception** tasks, we focus on recognizing *elements* in circuit schematics. We define an element as any component or device represented by a line in a netlist, such as transistors, resistors, subcircuit symbols, etc. As shown in Fig. 4, MLLMs are evaluated based on three key aspects:

1. Accuracy in Element Counting: This measures how well the model can identify and count the number of different elements in a schematic. We use tasks *type-wise counting* and *element classification*.

2. Precision in Identifying Connectivity: This assesses the model’s ability to accurately determine how elements are connected to each other. We use tasks *connection judgment* and *connection identification*, where connection judgment uses true-false questions to decide whether two elements are connected, and connection identification requires the model to state connecting elements.

3. Capability to Recognize the Entire Netlist: This evaluates whether the model can correctly identify the complete netlist of the circuit. We use task *topology*.

Accurate identification of elements, connectivity, and ports is fundamental to understanding and analyzing circuits. The complexity of element types and their connections in schematics makes this task particularly challenging. It requires the MLLM to have a more rigorous perception capability compared to traditional visual counting tasks.

The **analysis** tasks in AMSbench primarily assess the MLLMs’ comprehension of circuit schematics. This includes recognizing and analyzing the functions of circuits, as well as identifying key functional building blocks within them, as illustrated in Fig. 4. Beyond schematic understanding, the analysis tasks also cover other critical aspects of circuit design, such as interpreting signal waveforms, evaluating switching timing, and analyzing layout-related information. Additionally, we evaluate the understanding of AMS circuits, such as trade-offs between different circuit performance metrics by both LLMs and MLLMs. Accurately analyzing a circuit and its

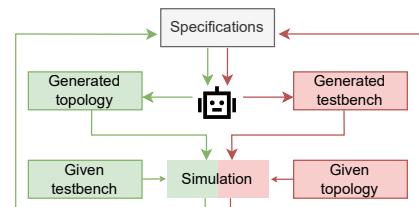

PREAMBLE: You are an analog integrated circuits expert.

TASK: Please generate a <circut> based on the given specification.

EXEMPLAR: SPICE netlist or PySPICE code

PROBLEM: specification

TASK: Please generate a testbench based on the given schematic and netlist.

EXEMPLAR: SPICE testbench netlist or PySPICE code

PROBLEM: schematic image, netlist, metric

Figure 5: Design task flow

270 corresponding performance metrics is the foundation for ensuring accurate and effective circuit

271 design.

272

273 The **design** tasks in our study consider both circuit design and testbench design, as shown in Fig. 5.

274 Proper circuit design ensures that the functionality meets specifications, while effective testbench

275 design guarantees that the circuit’s performance can be accurately measured and validated. These two

276 tasks are central to the AI-driven automation of AMS circuit design. In setting up the circuit design

277 tasks, we adopt and expand upon the benchmark established by AnalogCoder (Lai et al., 2025).

278

279 **Difficulty Levels** We classify the questions into three difficulty levels. Specifically, for the **perception**-

280 task, we categorize the difficulty based on the number of elements in the circuit: simple (num <

281 9), medium (9 < num < 16), and difficult (num > 16). For circuit functionality **analysis**, we classify

282 the problems according to the circuit type and group them into two levels based on their appearance

283 in educational stages: undergraduate and graduate levels. For testing the trade-offs between circuit

284 performances, we assign a classification suitable for engineers. For the **design** task, we classify the

285 circuits based on their complexity into three levels: simple, complex, and system-level circuits.

286

287 Table 2: Circuit design tasks. Number of (**simple** / **complex** / **system-level**) tasks are shown for each circuit type.

| Circuit Type   | # of Tasks | Circuit Type   | # of Tasks | Circuit Type    | # of Tasks | Circuit Type | # of Tasks |

|----------------|------------|----------------|------------|-----------------|------------|--------------|------------|

| Amplifier      | 7/0/0      | Oscillator     | 0/2/0      | Subtractor      | 0/1/0      | LDO          | 0/1/0      |

| Inverter       | 2/0/0      | Integrator     | 0/1/0      | Schmitt trigger | 0/1/0      | Comparator   | 0/1/0      |

| Current mirror | 2/0/0      | Differentiator | 0/1/0      | VCO             | 0/1/0      | PLL          | 0/0/1      |

| Op-amp         | 2/2/0      | Adder          | 0/1/0      | Bandgap         | 0/1/0      | SAR-ADC      | 0/0/1      |

291 Table 3: Testbench design tasks with number of metrics required per testbench suite.

| ID | Circuit Type                         | # of Metrics | ID | Circuit Type | # of Metrics | ID | Circuit Type       | # of Metrics |

|----|--------------------------------------|--------------|----|--------------|--------------|----|--------------------|--------------|

| 1  | Cross-coupled differential amplifier | 7            | 5  | PLL          | 2            | 9  | Unit capacitor     | 1            |

| 2  | Comparator                           | 2            | 6  | MOS_Ron      | 1            | 10 | Folded cascode OTA | 5            |

| 3  | Bootstrap                            | 1            | 7  | LDO          | 7            | 11 | SAR-ADC            | 1            |

| 4  | Telescopic cascode OTA               | 7            | 8  | VCO          | 2            | 12 | Bandgap            | 4            |

### 299 3.3 AMSBENCH STATISTICS

300 Fig. 4(a) illustrates the subtasks involved in the perception task along with the number of questions

301 at varying difficulty levels. Fig. 4(b) presents statistical information for the analysis task and its

302 various subtasks. The VQA tasks focus on evaluating the MLLM’s ability to interpret circuit-related

303 images, while the TQA tasks assess the model’s understanding of circuit knowledge and its awareness

304 of performance trade-offs. Table 2 and 25 present an overview of the design tasks for circuits and

305 testbenches, respectively. For the circuit design section, we incorporated the benchmarks provided

306 by AnalogCoder (Lai et al., 2025) and further extended them with additional circuit tasks, including

307 system-level circuit design. The testbench design tasks address a notable gap in the current community

308 by introducing a previously underexplored category.

## 310 4 EXPERIMENTS

### 312 4.1 MODELS

314 We perform experiments on mainstream closed-source MLLMs: GPT-4o (Hurst et al., 2024), Grok-

315 3 (gro, 2025), Gemini-2.5-pro (Team et al., 2023), Claude3.7 sonnet (Anthropic, 2024), Doubao-

316 1.5-vision-pro-32k (Guo et al., 2025b), and powerful open-source models: Kimi-VL (Team et al.,

317 2025), Qwen2.5-VL 72B (Yang et al., 2024a), DeepSeek-R1 (Guo et al., 2025a). We evaluate both

318 TQA tasks on all models, and VQA tasks on all models except DeepSeek-R1. We use all open-source

319 models with default parameters and deploy on up to 8 A100 GPUs.

320

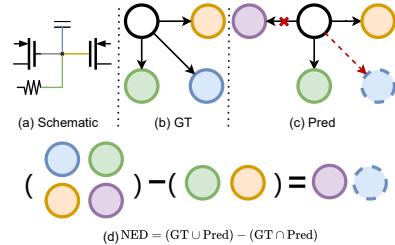

### 321 4.2 METRICS

322 For multiple-choice questions, we adopt accuracy (ACC) as the evaluation metric. For multiple-

323 selection questions, we use the F1 score. For netlist recognition tasks, we define a Netlist Edit

324 Distance (NED) as the evaluation metric, with the calculation procedure illustrated in Fig. 6. The

325 NED for each schematic image is normalized as shown in (1):

326

$$\text{NED}_{norm} = \frac{|\text{GT} \cup \text{Pred}| - |\text{GT} \cap \text{Pred}|}{|\text{GT}|} \quad (1)$$

327 For evaluating the circuit design tasks, we use  $\text{pass}@k$  as

328 the primary metric to measure the success rate of model-

329 generated circuits.  $\text{Syntax}@k$  and  $\text{Metric}@k$  are employed

330 to evaluate the generated testbenches.  $\text{Syntax}@k$  examines

331 the presence of syntactic errors that hinder simulation, and

332  $\text{Metric}@k$  verifies the functional correctness of the corre-

333 sponding test circuits.

334

### 336 4.3 EXPERIMENTAL RESULTS

337 **Perception Tasks:** Table 4 presents the models’ performance on fundamental circuit schematic

338 recognition tasks. Specifically, component counting and classification, both of which are essential for

339 accurate netlist extraction. Gemini achieves the best overall results. However, due to the complexity

340 and diversity of component types, the models show limitations in accurate counting. For element

341 type classification, Gemini performs well, reaching 94% accuracy. Among open-source models,

342 Qwen2.5-VL achieves 86%, suggesting that open-source models still have room for improvement in

343 component type recognition.

344

345 The lower part of Table 4 presents the accuracy of MLLMs in identifying inter-device connectivity.

346 While the models can produce reasonably accurate predictions for local connections, they fall short

347 in reconstructing the complete netlist. Even netlists produced by the best-performing model, Gemini,

348 require substantial modifications to align with the ground truth. Closed-source models perform

349 significantly better on these tasks, whereas Kimi-VL fail to produce outputs in the correct format.

350

351 Table 4: Comprehensive comparison of models across perception tasks and circuit interconnect recognition.

352 Abbreviations adopted: Ele. Cls = Element Classification, Loc. Desc = Location Description, Conn. Judg =

353 Connection Judgment, Conn. Ident = Connection Identification.

| 354 <b>Models</b>     | 355 <b>Total Counting</b> |                    | 356 <b>Type Counting</b> |                    | 357 <b>Ele. Cls</b>    |

|-----------------------|---------------------------|--------------------|--------------------------|--------------------|------------------------|

|                       | 358 <b>ACC (↑)</b>        | 359 <b>MSE (↓)</b> | 360 <b>ACC (↑)</b>       | 361 <b>MSE (↓)</b> |                        |

| Gemini-2.5-pro        | <b>0.65</b>               | <b>10.02</b>       | <b>0.64</b>              | <b>13.41</b>       | <b>0.94</b>            |

| GPT-4o                | 0.51                      | 19.05              | 0.54                     | 28.18              | 0.91                   |

| Claude-3.7-sonnet     | 0.36                      | 18.38              | 0.55                     | 24.18              | 0.83                   |

| Grok-3                | 0.22                      | 60.71              | 0.50                     | 26.48              | 0.84                   |

| Doubao-1.5-vision-pro | 0.24                      | 38.13              | 0.51                     | 24.76              | 0.93                   |

| Kimi-VL-A3B           | 0.15                      | 49.19              | 0.44                     | 34.96              | 0.66                   |

| Qwen2.5-VL-72B        | 0.43                      | 19.59              | 0.49                     | 18.59              | 0.86                   |

| 363 <b>Models</b>     | 364 <b>Loc. Desc</b>      |                    | 365 <b>Conn. Judg</b>    |                    | 366 <b>Conn. Ident</b> |

|                       | 367 <b>ACC (↑)</b>        | 368 <b>ACC (↑)</b> | 369 <b>F1 (↑)</b>        | 370 <b>NED (↓)</b> |                        |

| Gemini-2.5-pro        | <b>0.61</b>               | <b>0.85</b>        | <b>0.88</b>              | <b>0.91</b>        | –                      |

| GPT-4o                | 0.37                      | 0.73               | 0.65                     | 1.40               | –                      |

| Claude-3.7-sonnet     | 0.48                      | 0.76               | 0.71                     | 1.65               | –                      |

| Grok-3                | 0.50                      | 0.70               | 0.65                     | 1.84               | –                      |

| Doubao-1.5-vision-pro | 0.45                      | 0.76               | 0.64                     | 1.57               | –                      |

| Kimi-VL-A3B           | 0.31                      | 0.53               | 0.53                     | –                  | –                      |

| Qwen2.5-VL-72B        | 0.56                      | 0.77               | 0.52                     | 2.38               | –                      |

372 **Analysis Tasks:** Table 5 summarizes the models’ capabilities of analyzing AMS circuits. In

373 schematic interpretation(*Reasoning, Partition, Caption, Function*), different MLLMs exhibit distinct

374 strengths: Gemini demonstrates the highest accuracy in identifying and analyzing functional building

375 blocks, while Claude-Sonnet provides more accurate overall descriptions of circuit behavior. Gemini

376 also demonstrated strong performance on other circuit-related images. Table 16 shows that current

377 models can achieve relatively high accuracy in analyzing circuit knowledge designed for undergradu-

ate and graduate education. However, they perform poorly in understanding the trade-offs between

378 Figure 6: Edit distance computation be-

379 tween the GT and the predicted netlist.

380

378

379 Table 5: Comparison of models on analysis tasks

380

381

| 382 <b>Models</b>     | <b>Reasoning</b> | <b>Signal wave</b> | <b>Switching timing</b> | <b>Electrical characteristic</b> | <b>Layout</b> |

|-----------------------|------------------|--------------------|-------------------------|----------------------------------|---------------|

|                       | 383 ACC (↑)      | 384 ACC (↑)        | 385 ACC (↑)             | 386 ACC (↑)                      | 387 ACC (↑)   |

| Gemini-2.5-pro        | <b>0.92</b>      | <b>0.94</b>        | <b>0.96</b>             | <b>0.92</b>                      | 0.75          |

| GPT-4o                | 0.77             | 0.74               | 0.79                    | 0.80                             | 0.65          |

| Claude-3.7-sonnet     | 0.91             | 0.86               | 0.87                    | <b>0.92</b>                      | <b>0.83</b>   |

| Grok-3                | 0.61             | 0.84               | 0.85                    | 0.82                             | 0.63          |

| Doubao-1.5-vision-pro | 0.83             | 0.89               | 0.83                    | 0.85                             | 0.75          |

| Kimi-VL-A3B           | 0.74             | 0.64               | 0.59                    | 0.53                             | 0.58          |

| Qwen2.5-VL-72B        | 0.82             | 0.77               | 0.82                    | 0.85                             | 0.60          |

| 388 <b>Models</b>     | <b>Partition</b> | <b>Caption</b> | <b>Function (text)</b> | <b>Function (image)</b> | <b>TQA</b>  |

|-----------------------|------------------|----------------|------------------------|-------------------------|-------------|

|                       | 389 F1 (↑)       | 390 ACC (↑)    | 391 ACC (↑)            | 392 ACC (↑)             | 393 ACC (↑) |

| Gemini-2.5-pro        | <b>0.80</b>      | 0.70           | <b>0.95</b>            | <b>0.94</b>             | 0.72        |

| GPT-4o                | 0.57             | 0.61           | 0.93                   | 0.89                    | <b>0.78</b> |

| Claude-3.7-sonnet     | 0.64             | <b>0.98</b>    | 0.88                   | 0.74                    | 0.74        |

| Grok-3                | 0.59             | 0.41           | 0.77                   | 0.22                    | 0.74        |

| Doubao-1.5-vision-pro | 0.60             | 0.70           | 0.94                   | 0.93                    | 0.76        |

| Kimi-VL-A3B           | 0.25             | 0.71           | 0.59                   | 0.28                    | 0.59        |

| Qwen2.5-VL-72B        | 0.45             | 0.78           | 0.78                   | 0.85                    | 0.69        |

395

396

397 circuit performance metrics commonly encountered in industry. Even the best-performing model,

398 GPT-4o, only achieves 58% accuracy, indicating that LLMs currently lack a clear understanding of

399 the expected performance characteristics of each circuit in the design process.

400 **Design Tasks:** Table 6 shows the performance of the models in circuit design and testbench design

401 tasks. For circuit design, Grok-3 and Claude-Sonnet achieve the best results. However, for testbench

402 design, none of the current models can directly generate syntactically correct testbenches, with only

403 occasionally exceptions of GPT-4o. One possible reason is that the current pretraining data lacks

404 sufficient testbench-related knowledge. Additionally, the metrics that need to be measured vary across

405 different circuits, making testbench generation highly challenging.

406

407 Table 6: Comparison of models and circuit design and testbench design tasks. The data presents the average

408 results of all the circuits listed in Table 2. Detailed results are available in the appendix in Tables 18-27. *Syntax*:

409 generated testbench is syntactically correct to run simulation. *Metric*: generated testbench is topologically and

410 parametrically correct and produces the correct performance metric.

| 411 <b>Model</b>      | <b>Circuit Design</b> |             |             | <b>Testbench Design</b> |              |

|-----------------------|-----------------------|-------------|-------------|-------------------------|--------------|

|                       | 412 Pass@3            | 413 Pass@5  | 414 Pass@10 | 415 Syntax@5            | 416 Metric@5 |

| Gemini-2.5-pro        | 0.57                  | 0.54        | 0.43        | 0                       | 0            |

| GPT-4o                | 0.47                  | 0.49        | 0.42        | <b>0.084</b>            | 0            |

| Claude-3.7-sonnet     | 0.63                  | <b>0.64</b> | 0.50        | 0                       | 0            |

| Grok-3                | <b>0.65</b>           | 0.54        | <b>0.61</b> | 0                       | 0            |

| Doubao-1.5-vision-pro | 0.45                  | 0.24        | 0.15        | 0                       | 0            |

| Qwen2.5-VL-72B        | 0.47                  | 0.41        | 0.33        | 0                       | 0            |

| Kimi-VL-A3B           | 0.41                  | 0.25        | 0.13        | 0                       | 0            |

| DeepSeek-R1           | 0.55                  | 0.51        | 0.45        | -                       | -            |

## 420 421 5 CHALLENGES AND POSSIBLE IMPROVEMENTS

423

424 **Challenges of MLLMs in the interpretation of circuit-related images.** Existing MLLMs remain

425 limited in accurately interpreting circuit schematics. Although some models can capture localized

426 connectivity patterns, their performance degrades when extracting complete netlists. A key challenge

427 lies in the domain gap between circuit schematics and the natural images typically used in MLLM

428 pretraining, which leads to misclassification of components—for example, failing to distinguish

429 between PMOS and NMOS transistors. In addition, MLLMs often struggle to correctly associate

430 pins and ports with their parent components, resulting in connectivity errors.

431 To enhance model’s recognition capability, one approach is to combine MLLMs with specialized

432 vision models such as object detection (Bhandari et al., 2025) or OCR, which improves baseline

432 component recognition but does not fundamentally advance the MLLMs themselves. A more

433 promising direction is the construction of large-scale circuit-specific multimodal datasets, enabling

434 continual pretraining and post-training. We have conducted experiments on component grounding,

435 and the results show that MLLMs trained with such data exhibit improved perception of circuit

436 schematics, as illustrated in the Fig. 37.

437

438 **Hallucinations in circuit analysis.** In circuit analysis tasks, one major reason for poor performance

439 lies in the inability of the vision encoder to accurately and comprehensively embed visual

440 information, as discussed earlier. Another reason is the insufficient circuit-related knowledge of the

441 models themselves, which is also evident in text-only evaluation tasks. In existing works that combine

442 LLMs with AMS circuit design, LLMs are typically employed as analysis tools for downstream

443 design (Yin et al., 2024; Wei et al., 2025). A model with strong circuit analysis capabilities can

444 significantly reduce the parameter search space and partition the circuit into macros, thereby enabling

445 efficient layout generation. However, current models still lack the ability to accurately quantify

446 the trade-offs between circuit performance metrics, which limits their capability to recommend

447 appropriate circuit topologies under given target specifications.

448 One possible solution to enhance model performance in analysis tasks is to construct high-quality

449 datasets for training. However, due to the scarcity of documents related to circuit analysis and

450 design, training outcomes cannot be guaranteed. Another promising approach is to adopt Retrieval-

451 Augmented Generation (RAG), which dynamically collects high-quality multimodal data, cleans

452 it, and stores it in a vector database. During circuit analysis, the model can then retrieve relevant

453 knowledge from this database to support its reasoning and responses.

454 **Struggles in AMS circuit design.** Applying LLMs to AMS design involves three key stages:

455 topology design, testbench generation, and circuit sizing. End-to-end generation of directly usable

456 circuits remains highly challenging. For **topology design**, the primary requirement is to generate

457 novel yet functional circuits. Possible solutions include continual training of LLMs, combined with

458 prompt engineering. However, for complex and system-level circuits, directly producing a correct

459 design remains extremely challenging, as illustrated in Fig. 35. A divide-and-conquer strategy, where

460 submodules are designed and validated individually before integration, offers a more feasible path.

461 For **testbench generation**, the process is relatively standardized. Although it is still difficult to directly

462 generate usable testbenches, one feasible approach is leveraging predefined libraries and letting LLMs

463 perform targeted modifications. For **circuit sizing**, it is extremely difficult for an LLM to directly

464 produce circuits with desired sizing. One potential solution is to combine LLMs with traditional

465 black-box optimization algorithms, embedding domain knowledge into the optimization process to

466 accelerate convergence. Another promising approach is the use of multi-agent systems, where LLMs

467 emulate the workflow of human engineers. The former approach enables exploration of a broader

468 design space, albeit at the expense of efficiency, while the latter offers improved interpretability and

469 transparency, but the accumulation of hallucinations from each agent may negatively affect the final

470 performance.

## 471 6 CONCLUSION

472

473 This paper introduces AMSbench, a benchmark designed to evaluate the capabilities of MLLMs in the

474 AMS circuit domain. The benchmark comprehensively assesses model performance across three key

475 dimensions—schematic perception, circuit analysis, and circuit design—covering a variety of tasks.

476 AMSbench reveals significant limitations in current MLLMs, especially in schematic perception and

477 complex circuit design. While certain models perform adequately in basic component recognition

478 and simpler circuit analysis tasks, they notably struggle with advanced tasks, including accurate

479 schematic interpretation and system-level circuit design. Given the increasing interest in applying

480 MLLMs to automate AMS design processes, AMSbench provides an essential evaluation framework,

481 establishing a robust foundation for future advancements in this field. Achieving high-performance

482 scores on AMSbench would signify substantial progress and tangible benefits in the automation

483 of AMS circuit design. Future research will prioritize the expansion of datasets to enhance the

484 robustness and generalizability of multimodal models. It will investigate advanced methodologies,

485 such as RAG and RLHF, to augment design capabilities.

486     **REPRODUCIBILITY STATEMENT**

487

488     We provide the complete examples of AMSbench in the Appendix C, and release the full evaluation

489     dataset at the provided anonymous URL to facilitate reproducibility.

490

491

492

493

494

495

496

497

498

499

500

501

502

503

504

505

506

507

508

509

510

511

512

513

514

515

516

517

518

519

520

521

522

523

524

525

526

527

528

529

530

531

532

533

534

535

536

537

538

539

540 REFERENCES

541542 Grok 3 beta—the age of reasoning agents. <https://x.ai/blog/grok-3>, 2025. Accessed:

543 2025-05-14.544 Phillip E Allen and Douglas R Holberg. *CMOS Analog Circuit Design*. Elsevier, 2011.545 Anthropic. Introducing claude 3.7 sonnet. <https://www.anthropic.com/news/>, 2024.

546 Accessed: 2025-05-14.547 Jitendra Bhandari, Vineet Bhat, Yuheng He, Hamed Rahmani, Siddharth Garg, and Ramesh Karri.

548 Masala-chai: A large-scale spice netlist dataset for analog circuits by harnessing ai, 2025. URL

549 <https://arxiv.org/abs/2411.14299>.550 Jason Blocklove, Siddharth Garg, Ramesh Karri, and Hammond Pearce. Chip-chat: Challenges and

551 opportunities in conversational hardware design. In *2023 ACM/IEEE 5th Workshop on Machine

552 Learning for CAD (MLCAD)*, pp. 1–6. IEEE, 2023.553 Jayeeta Chaudhuri, Dhruv Thapar, Arjun Chaudhuri, Farshad Firouzi, and Krishnendu Chakrabarty.

554 SPICED+: Syntactical Bug Pattern Identification and Correction of Trojans in A/MS Circuits

555 Using LLM-Enhanced Detection. *IEEE Transactions on Very Large Scale Integration (VLSI)

556 Systems*, 2025.557 Zihao Chen, Jiangli Huang, Yiting Liu, Fan Yang, Li Shang, Dian Zhou, and Xuan Zeng. Artisan:

558 Automated Operational Amplifier Design via Domain-specific Large Language Model. In *2024

559 61th ACM/IEEE Design Automation Conference (DAC)*, pp. 1–6, 2024.560 Can Cui, Yunsheng Ma, Xu Cao, Wenqian Ye, Yang Zhou, Kaizhao Liang, Jintai Chen, Juanwu

561 Lu, Zichong Yang, Kuei-Da Liao, et al. A Survey on Multimodal Large Language Models for

562 Autonomous Driving. In *Proceedings of the IEEE/CVF Winter Conference on Applications of

563 Computer Vision*, pp. 958–979, 2024.564 Wenji Fang, Jing Wang, Yao Lu, Shang Liu, Yuchao Wu, Yuzhe Ma, and Zhiyao Xie. A survey of

565 circuit foundation model: Foundation ai models for vlsi circuit design and eda. *arXiv preprint

566 arXiv:2504.03711*, 2025.567 Yonggan Fu, Yongan Zhang, Zhongzhi Yu, Sixu Li, Zhifan Ye, Chaojian Li, Cheng Wan, and

568 Yingyan Celine Lin. Gpt4aigchip: Towards next-generation ai accelerator design automation via

569 large language models. In *2023 IEEE/ACM International Conference on Computer Aided Design

570 (ICCAD)*, pp. 1–9. IEEE, 2023.571 Jian Gao, Weidong Cao, Junyi Yang, and Xuan Zhang. AnalogGenie: A Generative Engine for

572 Automatic Discovery of Analog Circuit Topologies. *arXiv preprint arXiv:2503.00205*, 2025.573 Paul R Gray, Paul J Hurst, Stephen H Lewis, and Robert G Meyer. *Analysis and Design of Analog

574 Integrated Circuits*. John Wiley & Sons, 2009.575 Daya Guo, Dejian Yang, Haowei Zhang, Junxiao Song, Ruoyu Zhang, Runxin Xu, Qihao Zhu,

576 Shirong Ma, Peiyi Wang, Xiao Bi, et al. Deepseek-r1: Incentivizing reasoning capability in llms

577 via reinforcement learning. *arXiv preprint arXiv:2501.12948*, 2025a.578 Dong Guo, Faming Wu, Feida Zhu, Fuxing Leng, Guang Shi, Haobin Chen, Haoqi Fan, Jian Wang,

579 Jianyu Jiang, Jiawei Wang, et al. Seed1. 5-VL Technical Report. *arXiv preprint arXiv:2505.07062*,

580 2025b.581 Yunzhuo Hao, Jiawei Gu, Huichen Will Wang, Linjie Li, Zhengyuan Yang, Lijuan Wang, and

582 Yu Cheng. Can MLLMs Reason in Multimodality? EMMA: An Enhanced MultiModal ReAsoning

583 Benchmark. *arXiv preprint arXiv:2501.05444*, 2025.584 Aaron Hurst, Adam Lerer, Adam P Goucher, Adam Perelman, Aditya Ramesh, Aidan Clark, AJ Os-

585 trow, Akila Welihinda, Alan Hayes, Alec Radford, et al. Gpt-4o system card. *arXiv preprint

586 arXiv:2410.21276*, 2024.

594 Yao Lai, Sungyoung Lee, Guojin Chen, Souradip Poddar, Mengkang Hu, David Z Pan, and Ping Luo.

595 Analogcoder: Analog circuit design via training-free code generation. In *Proceedings of the AAAI*

596 *Conference on Artificial Intelligence*, volume 39, pp. 379–387, 2025.

597 Chengjie Liu, Weiyu Chen, Anlan Peng, Yuan Du, Li Du, and Jun Yang. AmpAgent: An LLM-based

598 Multi-Agent System for Multi-stage Amplifier Schematic Design from Literature for Process and

599 Performance Porting. *arXiv preprint arXiv:2409.14739*, 2024.

600 Mingjie Liu, Nathaniel Pinckney, Brucek Khailany, and Haoxing Ren. VerilogEval: Evaluating Large

601 Language Models for Verilog Code Generation. In *2023 IEEE/ACM International Conference on*

602 *Computer-Aided Design (ICCAD)*, 2023.

603 Pan Lu, Hritik Bansal, Tony Xia, Jiacheng Liu, Chunyuan Li, Hannaneh Hajishirzi, Hao Cheng,

604 Kai-Wei Chang, Michel Galley, and Jianfeng Gao. MathVista: Evaluating Math Reasoning in

605 Visual Contexts with GPT-4V, Bard, and Other Large Multimodal Models. *CoRR*, 2023.

606 Yao Lu, Shang Liu, Qijun Zhang, and Zhiyao Xie. RTLLM: An Open-Source Benchmark for

607 Design RTL Generation with Large Language Model. In *2024 29th Asia and South Pacific Design*

608 *Automation Conference (ASP-DAC)*, pp. 722–727. IEEE, 2024.

609 Long Ouyang, Jeffrey Wu, Xu Jiang, Diogo Almeida, Carroll Wainwright, Pamela Mishkin, Chong

610 Zhang, Sandhini Agarwal, Katarina Slama, Alex Ray, et al. Training language models to follow

611 instructions with human feedback. *Advances in neural information processing systems*, 35:27730–

612 27744, 2022.

613 Jingyu Pan, Guanglei Zhou, Chen-Chia Chang, Isaac Jacobson, Jiang Hu, and Yiran Chen. A Survey

614 of Research in Large Language Models for Electronic Design Automation. *ACM Transactions on*

615 *Design Automation of Electronic Systems*, 2025.

616 Behzad Razavi. *Design of Analog CMOS Integrated Circuits*. McGraw-Hill Higher Education, 2005.

617 Willy M Sansen. *Analog Design Essentials*, volume 859. Springer Science & Business Media, 2007.

618 Yichen Shi, Zhuofu Tao, Yuhao Gao, Tianjia Zhou, Cheng Chang, Yaxing Wang, Bingyu Chen,

619 Genhao Zhang, Alvin Liu, Zhiping Yu, et al. AMSnet-KG: A Netlist Dataset for LLM-based AMS

620 Circuit Auto-Design Using Knowledge Graph RAG. *arXiv preprint arXiv:2411.13560*, 2024.

621 Zhuofu Tao, Yichen Shi, Yiru Huo, Rui Ye, Zonghang Li, Li Huang, Chen Wu, Na Bai, Zhiping Yu,

622 Ting-Jung Lin, et al. Amsnet: Netlist dataset for ams circuits. In *2024 IEEE LLM Aided Design*

623 *Workshop (LAD)*, pp. 1–5. IEEE, 2024.

624 Gemini Team, Rohan Anil, Sebastian Borgeaud, Jean-Baptiste Alayrac, Jiahui Yu, Radu Soricut,

625 Johan Schalkwyk, Andrew M Dai, Anja Hauth, Katie Millican, et al. Gemini: a family of highly

626 capable multimodal models. *arXiv preprint arXiv:2312.11805*, 2023.

627 Kimi Team, Angang Du, Bohong Yin, Bowei Xing, Bowen Qu, Bowen Wang, Cheng Chen,

628 Chenlin Zhang, Chenzhuang Du, Chu Wei, et al. Kimi-VL Technical Report. *arXiv preprint*

629 *arXiv:2504.07491*, 2025.

630 Bin Wang, Chao Xu, Xiaomeng Zhao, Linke Ouyang, Fan Wu, Zhiyuan Zhao, Rui Xu, Kaiwen Liu,

631 Yuan Qu, Fukai Shang, et al. Mineru: An open-source solution for precise document content

632 extraction, 2024. URL <https://arxiv.org/abs/2409.18839>.

633 Ziming Wei, Zichen Kong, Yuan Wang, David Z Pan, and Xiyuan Tang. Toposizing: An llm-

634 aided framework of topology-based understanding and sizing for ams circuits. *arXiv preprint*

635 *arXiv:2509.14169*, 2025.

636 Zheyu Yan, Yifan Qin, Xiaobo Sharon Hu, and Yiyu Shi. On the viability of using llms for sw/hw

637 co-design: An example in designing cim dnn accelerators. In *2023 IEEE 36th International*

638 *System-on-Chip Conference (SOCC)*, pp. 1–6. IEEE, 2023.

639 An Yang, Baosong Yang, Beichen Zhang, Binyuan Hui, Bo Zheng, Bowen Yu, Chengyuan Li,

640 Dayiheng Liu, Fei Huang, Haoran Wei, et al. Qwen2. 5 technical report. *arXiv preprint*

641 *arXiv:2412.15115*, 2024a.

648 An Yang, Beichen Zhang, Binyuan Hui, Bofei Gao, Bowen Yu, Chengpeng Li, Dayiheng Liu,

649 Jianhong Tu, Jingren Zhou, Junyang Lin, et al. Qwen2. 5-Math Technical Report: Toward

650 Mathematical Expert Model via Self-Improvement. *arXiv preprint arXiv:2409.12122*, 2024b.

651

652 Yuxuan Yin, Yu Wang, Boxun Xu, and Peng Li. ADO-LLM: Analog Design Bayesian Optimization

653 with In-Context Learning of Large Language Models. *arXiv preprint arXiv:2406.18770*, 2024.

654

655 Xiang Yue, Yuansheng Ni, Tianyu Zheng, Kai Zhang, Ruqi Liu, Ge Zhang, Samuel Stevens, Dongfu

656 Jiang, Weiming Ren, Yuxuan Sun, et al. MMMU: A Massive Multi-Discipline Multimodal

657 Understanding and Reasoning Benchmark for Expert AGI. In *Proceedings of the IEEE/CVF

Conference on Computer Vision and Pattern Recognition*, pp. 9556–9567, 2024.

658

659 Renrui Zhang, Dongzhi Jiang, Yichi Zhang, Haokun Lin, Ziyu Guo, Pengshuo Qiu, Aojun Zhou,

660 Pan Lu, Kai-Wei Chang, Yu Qiao, et al. MathVerse: Does Your Multi-modal LLM Truly See the

661 Diagrams in Visual Math Problems? In *European Conference on Computer Vision*, pp. 169–186.

662 Springer, 2024.

663

664 Chenchen Zhao, Zhengyuan Shi, Xiangyu Wen, Chengjie Liu, Yi Liu, Yunhao Zhou, Yuxiang Zhao,

665 Hefei Feng, Yinan Zhu, Gwok-Waa Wan, et al. Mmcircuiteval: A comprehensive multimodal

666 circuit-focused benchmark for evaluating llms. *arXiv preprint arXiv:2507.19525*, 2025.

667

668 Li Zhong and Zilong Wang. Can LLM Replace Stack Overflow? A Study on Robustness and

669 Reliability of Large Language Model Code Generation. In *Proceedings of the AAAI Conference on

670 Artificial Intelligence*, volume 38, pp. 21841–21849, 2024.

671

672

673

674

675

676

677

678

679

680

681

682

683

684

685

686

687

688

689

690

691

692

693

694

695

696

697

698

699

700

701