# Toward Engineering AGI: Benchmarking the Engineering Design Capabilities of LLMs

Xingang  $Guo^{1*\dagger}$ , Yaxin  $Li^{1*}$ , Xiangyi  $Kong^{1*}$ , Yilan  $Jiang^{1*}$ , Xiayu  $Zhao^{1*}$ , Zhihua  $Gong^{1*}$ , Yufan  $Zhang^{1*}$ , Daixuan  $Li^{1}$ , Tianle  $Sang^{1}$ , Beixiao  $Zhu^{1}$ , Gregory  $Jun^{1}$ , Yingbing  $Huang^{1}$ , Yiqi  $Liu^{1}$ , Yuqi  $Xue^{1}$ , Rahul Dev  $Kundu^{1}$ , Qi  $Jian Lim^{1}$ , Yizhou  $Zhao^{2}$ , Luke Alexander  $Granger^{1}$ , Mohamed Badr Younis $^{1}$ , Darioush  $Keivan^{1}$ , Nippun Sabharwal $^{1}$ , Shreyanka  $Sinha^{1}$ , Prakhar  $Agarwal^{1}$ ,  $Kojo Vandyck^{1}$ , Hanlin  $Mai^{1}$ , Zichen  $Wang^{1}$ , Aditya  $Venkatesh^{1}$ , Ayush  $Barik^{1}$ , Jiankun  $Yang^{1}$ , Chongying  $Yue^{1}$ , Jingjie  $He^{1}$ , Libin  $Wang^{1}$ , Licheng  $Xu^{1}$ , Hao  $Chen^{1}$ , Jinwen  $Wang^{1}$ , Liujun  $Xu^{1}$ , Rushabh Shetty $^{1}$ , Ziheng  $Guo^{1}$ , Dahui  $Song^{1}$ , Manvi  $Jha^{1}$ , Weijie  $Liang^{1}$ , Weiman  $Yan^{1}$ , Bryan  $Zhang^{1}$ , Sahil Bhandary  $Yangor^{1}$ , Jialiang  $Zhang^{1}$ , Rutva  $Yangor^{1}$ , Xinyi  $Yangor^{1}$ , Mithesh Ballae  $Yangor^{1}$ , Feize  $Yangor^{1}$ , Ruiling  $Yau^{1}$ , Yifan  $Yangor^{1}$ , Yanfeng Ouyang $Yangor^{1}$ , Lianhui  $Yangor^{1}$ , Pavan  $Yangor^{1}$ , Pavan  $Yangor^{1}$ , Pavan  $Yangor^{1}$ , Pavan  $Yangor^{1}$ , Mayank  $Yangor^{1}$ , Mahdi  $Yangor^{1}$ , Huan  $Yangor^{1}$ , Bin  $Yangor^{1}$ , Bin Yang

<sup>1</sup>University of Illinois at Urbana-Champaign, <sup>2</sup>University of Pennsylvania,

Project page: https://agi4engineering.github.io/Eng-Design/ Dataset page: https://huggingface.co/datasets/opt1zer/EngDesign

## **Abstract**

Modern engineering, spanning electrical, mechanical, aerospace, civil, and computer disciplines, stands as a cornerstone of human civilization and the foundation of our society. However, engineering design poses a fundamentally different challenge for large language models (LLMs) compared with traditional textbook-style problem solving or factual question answering. Although existing benchmarks have driven progress in areas such as language understanding, code synthesis, and scientific problem solving, real-world engineering design demands the synthesis of domain knowledge, navigation of complex trade-offs, and management of the tedious processes that consume much of practicing engineers' time. Despite these shared challenges across engineering disciplines, no benchmark currently captures the unique demands of engineering design work. In this work, we introduce **ENGDESIGN**, an **Eng**ineering **Design** benchmark that evaluates LLMs' abilities to perform practical design tasks across nine engineering domains. Unlike existing benchmarks that focus on factual recall or question answering, ENGDESIGN uniquely emphasizes LLMs' ability to synthesize domain knowledge, reason under constraints, and generate functional, objective-oriented engineering designs. Each task in ENGDESIGN represents a real-world engineering design problem, accompanied by a detailed task description specifying design goals, constraints, and performance requirements. ENGDESIGN pioneers a simulation-based evaluation paradigm that moves beyond textbook knowledge to assess genuine engineering design capabilities and shifts evaluation from static answer checking to dynamic, simulation-driven functional verification, marking a crucial step toward realizing the vision of engineering Artificial General Intelligence (AGI).

## 1 Introduction

Modern engineering, spanning electrical, mechanical, aerospace, civil, and computer disciplines [Chen, 2004, Grote and Hefazi, 2021, Chen and Liew, 2002, Blockley, 2012], stands as a cornerstone of human civilization and the foundation of our society. From the electrical grids powering our cities to the aerospace systems launching us beyond Earth, from analog integrated circuits forming the

<sup>&</sup>lt;sup>3</sup>University of California San Diego, <sup>4</sup>University of Michigan, <sup>5</sup>Amazon AGI

<sup>\*</sup>Core Contributors †Corresponding Author

foundation of electronics to the structural designs supporting our skylines, engineering disciplines have woven themselves into the fabric of human existence [Ten and Hou, 2024, Paul et al., 2023, Gray et al., 2009]. At its core, engineering design is the systematic and creative process that engineers use to solve problems and create functional products, systems, or processes, transforming requirements and constraints into tangible solutions that meet human needs. Recent advances in large language models (LLMs) have led to remarkable performance on conventional question-answering (QA) benchmarks, with strong results across a wide range of tasks—from textbook-level scientific problem solving [Rein et al., 2024, Wang et al., 2024b, Du et al., 2025, Zou et al., 2024], to code synthesis [Chen et al., 2021, Jain et al., 2024, Chan et al., 2024], and even to answering textbook-level questions across various engineering domains [Kevian et al., 2024, Li et al., 2024, Skelic et al., 2025]. Today, industry leaders aspire to build on such progress in LLMs to create general-purpose AI engineers capable of bringing to life humanity's boldest ambitions-from interstellar starships to Dyson spheres that harvest stellar energy-leveraging these foundation models' vast knowledge across engineering domains and their potential to transcend traditional disciplinary boundaries that constrain human engineers [Business Wire, 2025].

However, practical engineering design confronts LLMs with a grand challenge profoundly different and vastly more complex than conventional factual recall or textbook-level engineering problem solving. Specifically, real-world engineering design demands the synthesis of domain knowledge, navigation of complex trade-offs, management of the tedious processes that consume much of practicing engineers' time, and rigorous validation through domain-specific simulators to ensure that designs meet functional requirements and safety constraints. Yet despite progress in textbook-level engineering problem solving, no existing benchmark captures the distinctive demands of practical design work—with its multifaceted, open-ended challenges across multiple engineering disciplines.

In this work, we introduce ENGDESIGN, the first benchmark for holistically evaluating LLMs on real-world, multi-domain engineering design challenges. Unlike traditional Question-Answer (QA) formats, our benchmark requires models to function as practicing engineers, producing functional solutions, such as dynamical system controllers, material structure designs, analog integrated circuits, or GPU architectures that meet rigorous performance requirements. ENGDESIGN uniquely emphasizes the synthesis of domain knowledge, constraint-based reasoning, and the generation of functional, objective-oriented designs, spanning practical design problems across nine engineering domains: Operating System Design, Computer Architecture Design, Control System Design, Mechanical Systems, Structural Design, Digital Hardware Design, Analog Integrated Circuit Design, Robotics, and Signal Processing. Each task in ENGDESIGN is accompanied by an executable evaluation pipeline that validates designs against task requirements using domain-specific simulation tools such as SPICE simulations [Roberts, 1996], structural finite element analysis [Bhavikatti, 2005], MATLAB Control System Toolbox [Chiang and Safonov, 1984], and other scientific software tailored to specific engineering domains. Our approach establishes a revolutionary evaluation paradigm: assessment using engineering simulation tools. This simulation-based approach fundamentally shifts evaluation from linguistic pattern matching to functional verification, ensuring that solutions are assessed based on their engineering merit rather than textual plausibility.

ENGDESIGN advances LLM evaluation methodology by moving beyond conventional questionanswering benchmarks to address the open-ended, constraint-driven nature of real-world engineering design. Our key contributions include:

- The first multi-domain engineering design benchmark. Unlike QA benchmarks that test narrow factual or procedural knowledge, ENGDESIGN evaluates LLMs on complex engineering design challenges spanning diverse engineering disciplines (e.g., mechanical, electrical, civil), requiring synthesis of domain knowledge, constraint satisfaction, and strong reasoning capabilities.

- Executable simulation-based evaluation. We replace static correctness checks with dynamic, domain-specific evaluation pipelines. Each task includes human-designed task-specific evaluation scripts that rigorously verify functional feasibility (e.g., via simulation, constraint validation, or performance testing), ensuring objective, reproducible scoring grounded in real engineering standards.

- Partial-credit grading for incomplete solutions. Conventional benchmarks often use binary scoring, but ENGDESIGN's rubrics quantify incremental progress (e.g., 20/100 for

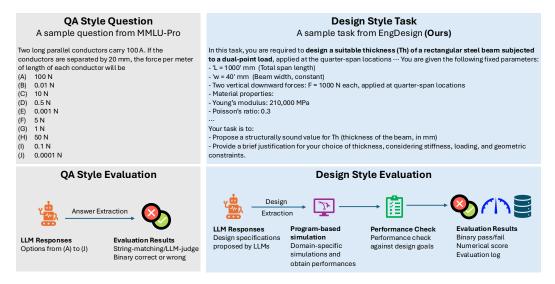

Figure 1: Comparison between conventional QA-style benchmarks (left) and the design-style benchmark ENGDESIGN (right). Conventional QA benchmarks evaluate LLMs through static answer extraction and string-matching, while ENGDESIGN involves open-ended design tasks with potentially non-unique solutions. LLMs must propose candidate design specifications, which are evaluated via program-based simulations and performance validation pipelines.

delivering a stable controller that meets partial performance requirements). This granularity reveals nuanced capability gaps and rewards iterative refinement.

• Empirical validation of design competencies. Through large-scale evaluations across 10+ state-of-the-art LLMs including both general-purpose LLMs and reasoning models, we demonstrate ENGDESIGN's ability to expose critical limitations in AI systems—such as over-reliance on textual patterns or failure to handle trade-offs—that are invisible to traditional benchmarks.

We believe that ENGDESIGN marks a crucial milestone toward realizing engineering AGI by breaking new ground with its comprehensive coverage of engineering design problems across diverse domains, each requiring deep technical expertise and domain-specific simulation tools for rigorous evaluation. This benchmark not only measures what models know but what they can actually design, bridging the chasm between textbook-level knowledge understanding and practical engineering capability.

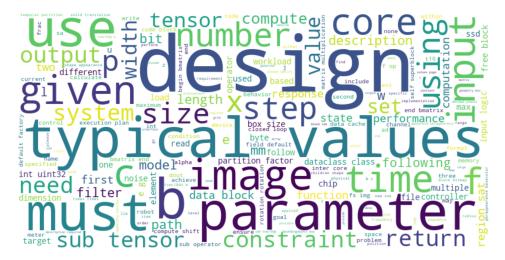

## 2 ENGDESIGN

In this section, we introduce ENGDESIGN, a multi-domain benchmark developed to evaluate the capabilities of LLMs in real-world engineering design tasks. Unlike conventional QA benchmarks, ENGDESIGN adopts a rigorous simulation-based evaluation pipeline to assess model performance in practical, design-oriented scenarios. Table 1 summarizes the benchmark's key statistics: it comprises 101 design tasks spanning 9 engineering domains, with a total of 473 gradable items. While the task distribution may appear uneven, it naturally reflects the domain expertise of our contributors and the filtering rigor imposed by our multi-stage review process. Notably, the average prompt length in ENGDESIGN is 778.71 tokens, substantially higher than typical QA benchmarks<sup>1</sup>, highlighting the contextual richness and complexity of realistic engineering design problems. Word clouds generated from ENGDESIGN prompts are provided in Appendix C.

Among the 101 tasks in ENGDESIGN, 34 tasks require domain-specific scientific software such as MATLAB or Cadence for evaluation, while the remaining 67 tasks are fully open-sourced and evaluated using manually authored evaluation scripts. We consolidate these tasks into a subset

<sup>&</sup>lt;sup>1</sup>We adopt Byte Pair Encoding (BPE) tokenizer for OpenAI models, available at Tiktoken. Token length comparison between EngDesign and other QA benchmarks in Appendix C.1.

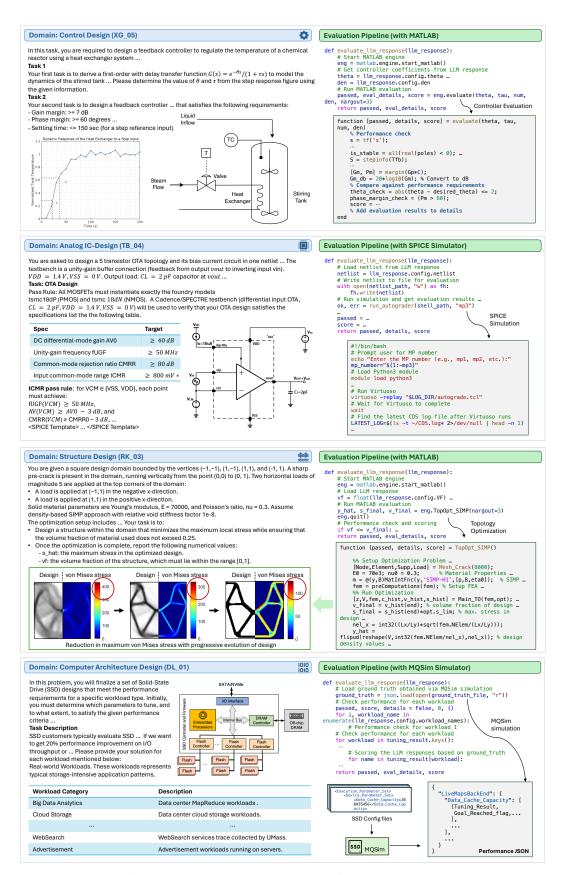

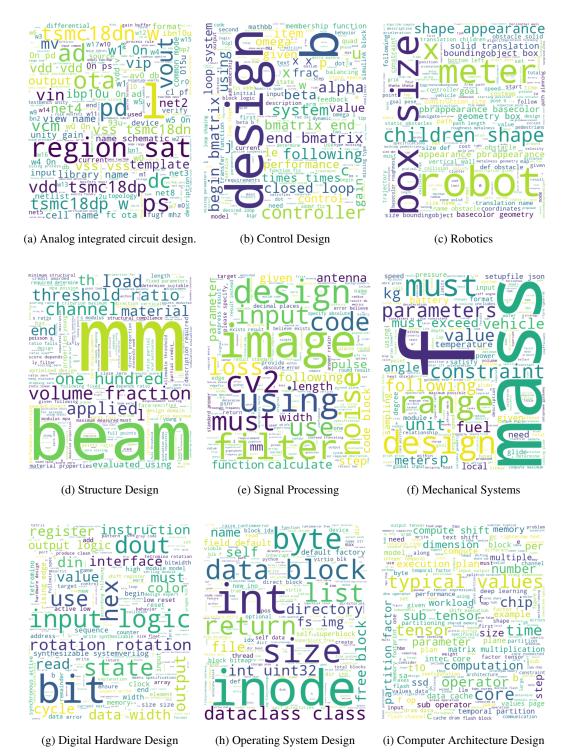

Figure 2: Selected demonstration tasks from ENGDESIGN.

| Table 1: Statistics of ENGDESIGN. Token counts are computed vis o200k base in Tiktoken | Table 1: Statistics of ENGDESIGN. | Token counts are computed a | vis o200k base in Tiktoken |

|----------------------------------------------------------------------------------------|-----------------------------------|-----------------------------|----------------------------|

|----------------------------------------------------------------------------------------|-----------------------------------|-----------------------------|----------------------------|

| <b>Engineering Domain</b> |      | # tasks |       | # rubrics | # (  | query to | okens   |

|---------------------------|------|---------|-------|-----------|------|----------|---------|

| =g                        | Open | Closed  | Total | 1401105   | Max  | Min      | Avg     |

| Operating System Design   | 8    | 0       | 8     | 66        | 2938 | 310      | 1103.25 |

| Computer Arch Design      | 5    | 0       | 5     | 20        | 4385 | 2348     | 3539.60 |

| Control Design            | 7    | 11      | 18    | 100       | 1361 | 209      | 634.44  |

| Mechanical Systems        | 6    | 1       | 7     | 32        | 781  | 225      | 391.14  |

| Structure Design          | 7    | 6       | 13    | 25        | 483  | 186      | 345.31  |

| Digital Hardware Design   | 13   | 4       | 17    | 58        | 1715 | 206      | 515.65  |

| Analog IC Design          | 0    | 5       | 5     | 23        | 2136 | 547      | 1196.6  |

| Robotics                  | 10   | 0       | 10    | 68        | 1485 | 192      | 771.9   |

| Signal Processing         | 11   | 7       | 18    | 81        | 2304 | 151      | 611.72  |

| Overall                   | 67   | 34      | 101   | 473       | 4385 | 151      | 778.71  |

called ENGDESIGN-OPEN to support broader community adoption without licensing constraints. Additionally, 23 tasks of ENGDESIGN incorporate images as part of the task input to LLMs.

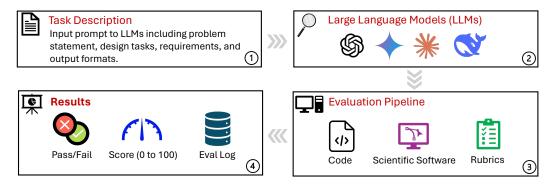

## 2.1 Task Structure

Each task of ENGDESIGN consists of the following four key components:

- 1. Task Description. This part is the query prompt fed into the LLMs, offering a clear and detailed definition of the engineering design problem, including design objectives, specifications, constraints.

- **2. Evaluation Rubrics.** Given the complexity of ENGDESIGN tasks, each task is further decomposed into multiple gradable items evaluated individually during the performance check stage. The evaluation rubrics define the assessment criteria and scoring metrics, with a full score of 100. This enables models to receive partial credit even if the design does not fully meet all specified requirements.

- **3. Evaluation Pipeline.** Each task includes automated evaluation scripts that assess the LLMs' design. It returns a binary pass/fail indicator, numerical score, and evaluation logs for further analysis.

- **4. Reference Design.** Each task provides a validated reference design that fully satisfies all specified requirements, ensuring the feasibility and realism of the design challenge.

Figure 2 shows four demonstrated design examples from ENGDESIGN including task descriptions and evaluation pipelines.

# 2.2 Evaluation Pipeline

Unlike conventional benchmarks, which often have a single golden answer that allows evaluation through exact string matching or LLM-as-judge scoring, our engineering design tasks inherently lack a unique *golden design*. For example, there are infinitely many valid controller designs that can regulate the temperature of a stirred tank modeled by a first-order system while satisfying both time-domain and frequency-domain performance requirements. To address this challenge, our benchmark introduces a **simulation-based evaluation pipeline**. Specifically, for each LLM-generated design, we first parse the key design components from the response automatically (such as code snippets, key parameters, etc.). These components are then fed into our evaluation pipeline, which runs domain-specific simulations to assess the design's performance against the specified task requirements. Guided by a per-task rubric table, the evaluation pipeline outputs three key results: a binary pass/fail indicator, a numerical score between 0 and 100, and a detailed log that records the evaluation process for further analysis. Below we discuss each step in detail.

**Structured Responses from LLMs.** To constrain the output format for a wide range of LLMs and ensure compatibility with our evaluation pipeline, we adopt the popular open-source Python library instructor [Liu and Contributors, 2024], which is built on top of Pydantic and facilitates structured LLM responses. By defining schema templates that specify expected fields, such as design parameters or code snippets, the instructor package enables LLMs to produce outputs in a pre-defined format. We provide an example at Figure 10 in Appendix D.2. Specifically, LLMs are instructed to construct

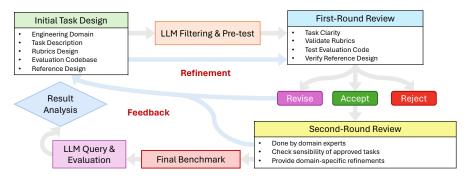

Figure 3: An overview of the construction process of ENGDESIGN, illustrating stages from initial task design, LLM filtering, and expert review to final benchmark integration, with iterative refinement and evaluation.

their responses into two main parts: (1) a reasoning field, which contains the step-by-step reasoning process for solving the task, and (2) a ConfigFile class, which summarizes the final design results, including their design choices or code snippets. During evaluation, the fields defined in ConfigFile can be automatically parsed to trigger the simulation-based evaluation pipeline.

**Task-Specific Evaluation Pipeline.** A simulation-based evaluation pipeline was designed for each task. For example, control engineering tasks may evaluate closed-loop dynamics through metrics such as rise time, settling time, overshoot, and phase/gain margins via MATLAB. The evaluation pipeline outputs three key results: (1) a binary pass/fail indicator for meeting all performance requirements, (2) a numerical score (0–100) reflecting fine-grained performance analysis, and (3) an evaluation log capturing simulation outputs, performance metrics, or error messages.

#### 2.3 Construction of ENGDESIGN

The construction of ENGDESIGN follows a multi-stage process that integrates both automated validation and human expertise as shown in Figure 3:

- Initial Task Design. We recruited graduate students and researchers from various engineering disciplines to contribute initial task proposals, drawing on open-source resources and their domain knowledge. Contributors were guided to follow a standardized submission format, which includes a task description, evaluation rubric, executable evaluation codebase, and a reference solution.

- 2. **LLM Filtering and Pre-Test.** Submitted tasks undergo an initial filtering phase using a language model (o4-mini) to assess prompt sufficiency and the functionality of the evaluation code. Specifically, we prompt the LLM to classify the task's engineering domain and determine whether the information provided is adequate to solve the problem. If the model flags missing or unclear details, we work with the original contributor to address those gaps.

- 3. **First-Round Review.** Tasks that pass the pre-test enter a first-round review involving close collaboration between reviewers and the original authors. The review ensures that:

- The task description is clear, self-contained, and complete.

- The evaluation rubric is well-defined with partial credit, and aligns with the task goals.

- The evaluation codebase is executable, robust, and handles typical edge cases.

- The reference design meets all performance requirements, validating the task feasibility.

Based on this review, tasks fall into one of three categories: **Accept**: the task meets all requirements and proceeds to expert review; **Revise**: minor issues are identified and addressed in collaboration with the contributor; or **Reject**: the task is excluded due to critical issues such as unfeasibility, triviality, or misalignment with design-oriented evaluation.

4. **Second-Round Review with Domain Experts.** Tasks accepted in the first round are reviewed by faculty experts in the corresponding engineering domain. These experts assess the technical soundness and relevance of each task to ensure it serves as a meaningful evaluation of LLMs in realistic design settings.

Table 2: Average pass rate (%) results (each task evaluated over 3 trials). \* Model is not multimodal and was evaluated only on the text-only subset. We report text-only results for all models in Appendix D.4. The domain abbreviations are: AICD = Analog Integrated Circuit Design, Arch = Computer Architecture Design, Ctrl = Control Design, DHD = Digital Hardware Design, Mech = Mechanical Systems, OS = Operating System Design, Robo = Robotics, SigP = Signal Processing, Stru = Structure Design. The best results for each column are highlighted in bold.

| Model               | Overall     | AICD | Arch  | Ctrl  | DHD   | Mech  | os    | Robo  | SigP  | Stru  |  |  |  |  |

|---------------------|-------------|------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| Model               | Overali     | AICD | AICH  | CIII  | שווט  | Mech  | US    | KUDU  | Sigi  | Situ  |  |  |  |  |

|                     | Chat Models |      |       |       |       |       |       |       |       |       |  |  |  |  |

| GPT-4o              | 15.68       | 0.00 | 20.00 | 18.52 | 10.26 | 0.00  | 4.17  | 26.67 | 17.65 | 25.64 |  |  |  |  |

| DeepSeek-v3*        | 17.92       | 0.00 | 0.00  | 27.27 | 25.64 | 0.00  | 0.00  | 16.67 | 12.82 | 38.89 |  |  |  |  |

| Gemini-2.0-Flash    | 14.16       | 0.00 | 0.00  | 15.15 | 16.67 | 4.76  | 0.00  | 20.00 | 5.13  | 36.11 |  |  |  |  |

| Claude-3.7-Sonnet   | 22.61       | 0.00 | 40.00 | 16.67 | 33.33 | 14.29 | 0.00  | 33.33 | 21.57 | 30.77 |  |  |  |  |

| Reasoning Models    |             |      |       |       |       |       |       |       |       |       |  |  |  |  |

| 01                  | 29.17       | 0.00 | 40.00 | 24.07 | 41.03 | 14.29 | 37.50 | 50.00 | 25.49 | 23.08 |  |  |  |  |

| 03                  | 34.38       | 0.00 | 40.00 | 35.19 | 20.51 | 23.81 | 25.00 | 63.33 | 41.18 | 30.77 |  |  |  |  |

| o3-high             | 33.57       | 0.00 | 40.00 | 27.78 | 20.51 | 28.57 | 30.43 | 68.97 | 35.29 | 41.03 |  |  |  |  |

| o4-mini             | 31.60       | 0.00 | 33.33 | 24.07 | 41.03 | 19.05 | 29.17 | 43.33 | 33.33 | 41.03 |  |  |  |  |

| o4-mini-high        | 34.04       | 0.00 | 40.00 | 27.78 | 47.22 | 19.05 | 37.50 | 46.67 | 35.29 | 35.90 |  |  |  |  |

| Gemini-2.5-Pro      | 29.54       | 0.00 | 0.00  | 33.33 | 43.59 | 0.00  | 9.52  | 56.67 | 12.82 | 50.00 |  |  |  |  |

| DeepSeek-R1*        | 25.53       | 0.00 | 36.36 | 36.36 | 38.46 | 4.76  | 5.26  | 26.67 | 20.51 | 41.67 |  |  |  |  |

| Claude-3.7-Thinking | 20.07       | 0.00 | 33.33 | 18.52 | 17.95 | 9.52  | 0.00  | 40.00 | 19.61 | 28.21 |  |  |  |  |

5. **Final Integration.** Tasks that pass both review stages are standardized to match the benchmark's formatting and structural guidelines, and are formally included in the ENGDESIGN.

# 3 Experiments

We evaluate a set of representative LLMs on the ENGDESIGN and analyze their performance.

**Evaluated LLMs.** For chat models, we include GPT-4o, Claude-3.7-Sonnet, Gemini-2.0-Flash, and DeepSeek-v3. For reasoning models, we evaluate o1, o3, o3-high, o4-mini, o4-mini-high, Claude-3.7-Thinking, DeepSeek-R1, and Gemini-2.5-Pro.

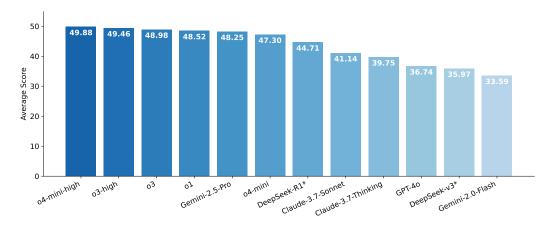

**Evaluation Metrics.** We report three primary evaluation metrics: (1) **Average Pass Rate**, (2) **Average Score**, and (3) **Reasoning Robustness**. Each task is evaluated over three independent trials per model. To measure reasoning robustness, we compute the ratio between the number of tasks where all three trials passed and the number of tasks where at least one trial passed. This ratio, which ranges from 0 to 1, serves as a straightforward indicator of an LLM's reasoning consistency. A value closer to 1 indicates higher robustness and more stable reasoning behavior across repeated runs. Formal definitions of all evaluation metrics are provided in Appendix D.3.

#### 3.1 Main Results

Table 2 presents the average pass rates and average score across evaluated LLMs, across 9 distinct engineering design areas. The average score demonstrates a strong correlation with the pass rate, which we provided the detailed results in Appendix D.4. We make the following key observations.

ENGDESIGN presents a highly challenging benchmark, with even the best-performing models achieving only modest pass rate. As shown in Table 2, no model surpasses a 35% overall pass rate. The top-performing model, o3, achieves 34.38%, while widely-used chat models such as GPT-40 and Gemini-2.0-Flash attain around 15%. Analog IC design tasks stands as the most difficult ones where all the models got 0% pass rate. These results highlight the difficulty of the benchmark, which stems from its requirements for domain-specific expertise, multi-step reasoning, and design trade-off considerations, capabilities that go beyond the strengths of current LLMs.

Reasoning models outperform general-purpose chat models. Models designed with enhanced reasoning capabilities, including o3, o4-mini, and DeepSeek-R1, consistently outperform general-purpose chat models across most engineering domains. However, this trend does not hold for Claude

Figure 4: Reasoning robustness distribution of evaluated LLMs on ENGDESIGN.

models, where both Claude-3.7-Sonnet and Claude-3.7-Thinking exhibit similar pass rates despite their differences in reasoning emphasis.

Reasoning Models are more robust in general. Figure 4 shows the reasoning robustness of all evaluated models. Reasoning-focused models such as o1, o3, and o4-mini-high achieve the highest robustness scores (0.62, 0.61, and 0.57, respectively), indicating strong consistency across repeated trials on tasks they are capable of solving. In contrast, chat-oriented models like Gemini-2.0-flash and DeepSeek-v3 exhibit substantially lower robustness (0.20 and 0.35), reflecting less stable reasoning behavior. Notably, the gap in reasoning robustness between top-performing reasoning models and weaker chat models is more pronounced than in average pass rate as shown in Table 2—up to a  $3\times$  performance difference in robustness compared to a  $2\times$  difference in pass rate. This highlights robustness as a distinguishing strength of reasoning models.

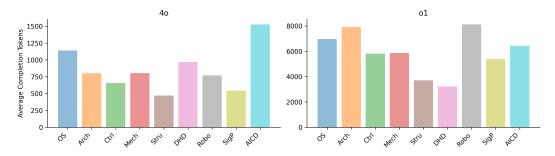

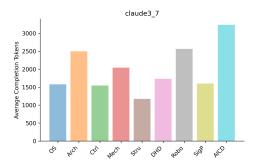

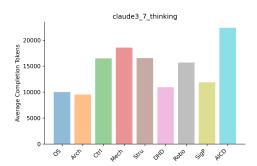

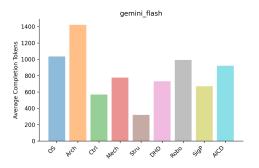

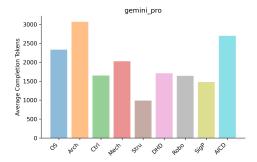

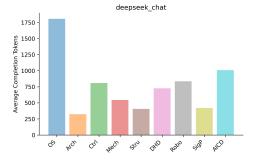

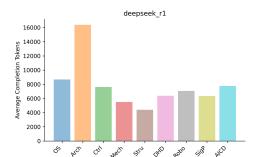

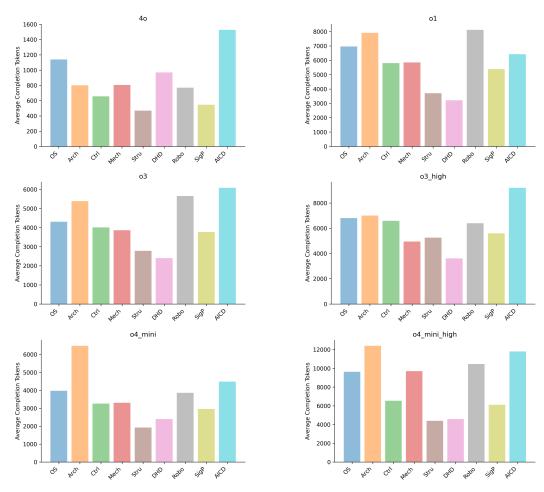

**Token Consumption**. Reasoning models require substantially more compute due to longer inference time. We analyze the number of completion tokens generated across different models. As shown in Figure 5, the reasoning model (o1) produces significantly more tokens than the non-reasoning model (GPT-40) to achieve performance gains. Optimizing the latency–performance trade-off will be essential for making future models more accessible and deployable in real-world engineering design scenarios. Additional results are provided in Appendix D.5.

Figure 5: Average token consumption of evaluated LLMs on ENGDESIGN.

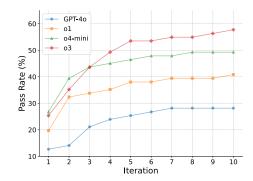

## 3.2 Iterative Design

To emulate the workflow of human engineers, we implement an iterative design protocol that allows LLMs to refine their solutions based on feedback from previous attempts. In our implementation, the LLM is provided with its previous design output along with corresponding evaluation results, such as scores, performance metrics, and diagnostic logs, and is then prompted to generate an improved design in the subsequent iteration. The prompt we used for iterative design is presented in Figure 6.

## **LLM Prompt for Iterative Design**

Task Description: original task description

Previous Responses: previous responses

Evaluation Feedback: previous evaluation results

**Instruction:** Please review the feedback above and propose an improved solution based on the evaluation results.

Figure 6: **Left**: LLM prompt for iterative design. **Right**: Average pass rate across iterations, showing how performance evolves with feedback-driven updates.

As shown in Figure 6, model performance consistently improves with additional iterations. Notably, o3 achieves almost a 60% pass rate after ten iterations.<sup>2</sup>. However, we also observed that iterative design does not help in all cases. For example, in Analog IC design tasks, models still fail to meet the requirements even after ten iterations.

#### 3.3 Failure Analysis

To better understand the limitations of LLMs in engineering design tasks, we define five primary error categories observed in ENGDESIGN:

- 1. **Domain Knowledge Error (DKE).** The model lacks essential engineering knowledge required to interpret or solve the task correctly.

- 2. Constraint Violation Error (CVE). The model generates designs that violate explicitly stated constraints, such as structural limits, performance bounds, or budgetary requirements.

- 3. **Prior Knowledge Overreliance (PKO).** The model applies memorized patterns or text-book solutions without adapting them to the specific requirements of the task, resulting in suboptimal or invalid outputs.

- 4. **Hallucination** (HAL). The model fabricates content, such as equations, parameters, or designs, that is unsupported by the task description or domain knowledge.

- 5. **Computation Error (CE).** The model performs arithmetic or symbolic computations incorrectly despite correct methodological reasoning.

- 6. Others. Residual errors that do not fit the above categories

|  |  | Table 3: | Error | types | statistics | for t | hree re | presentative | models. |

|--|--|----------|-------|-------|------------|-------|---------|--------------|---------|

|--|--|----------|-------|-------|------------|-------|---------|--------------|---------|

|                   | 71    |       |       |       |      |        |

|-------------------|-------|-------|-------|-------|------|--------|

| Model             | DKE   | CVE   | PKO   | HAL   | COM  | Others |

| o4-mini           | 33.3% | 25.2% | 18.8% | 12.6% | 9.0% | 0.9%   |

| Gemini-2.5-Pro    | 31.9% | 31.9% | 15.9% | 12.4% | 6.2% | 1.7%   |

| Claude-3.7-Sonnet | 30.7% | 36.0% | 10.5% | 13.2% | 7.0% | 2.6%   |

We analyzed the responses of three representative models (o4-mini, Gemini-2.5-Pro, and Claude-3.7-Sonnet) on ENGDESIGN tasks where they failed evaluation, and manually annotated each failure with its corresponding error types. The results are summarized in Table 3. Given the complexity of engineering design problems, many responses exhibited multiple failure modes; we therefore allowed multi-label annotations per task.

<sup>&</sup>lt;sup>2</sup>Due to time and resource constraints, the iterative design protocol was applied to a selected subset (71 tasks) of ENGDESIGN tasks using four representative models: GPT-40, o1, o3, and o4-mini. As a result, reported pass rates in the iterative experiments are slightly lower than the ones report in Table 2. Nonetheless, this subset demonstrates the effectiveness of feedback-driven refinement and highlights the potential of LLMs to improve design quality through iterative design.

Our analysis yields several key observations<sup>3</sup>:

- 1. Dominant failure modes: Insufficient domain knowledge and constraint violations together account for roughly 55–67% of all failures. This indicates that LLMs frequently struggle to apply domain-specific principles, satisfy task constraints, and generalize beyond memorized patterns.

- 2. Second-tier issues: Over-reliance on prior knowledge and hallucinations contribute 25–30%, suggesting that incorrect reuse or misapplication of known facts remains a significant challenge.

- **3. Low arithmetic fragility:** Pure computational errors are rare ( $\leq$ 9%), implying that numerical reasoning is not the primary bottleneck for current frontier models.

## 4 Related Work

Large Language Models. Advances in large language models (LLMs) have been propelled by scaling, instruction tuning, and improved reasoning. Frontier models such as GPT-3 and GPT-4 [Brown et al., 2020, Achiam et al., 2023], Claude [Anthropic, a], Gemini [Team et al., 2023], and DeepSeek [Liu et al., 2024a] exhibit broad general capabilities. Recent work enhances reasoning through architectural and prompting innovations, including Chain-of-Thought [Wei et al., 2022] and least-to-most prompting [Zhou et al., 2022]. These developments have led to reasoning-oriented models such as OpenAI's o-series [OpenAI], Claude-Thinking [Anthropic, b], Gemini 2.5 Pro [Google DeepMind], and DeepSeek-R1 [Guo et al., 2025]. Yet, their effectiveness in domain-specific contexts, particularly engineering design, remains largely unexplored. ENGDESIGN fills this gap by evaluating LLMs within realistic, simulation-based engineering workflows.

General Purpose Benchmarks for LLMs. A variety of benchmarks assess LLM reasoning and problem-solving capabilities. MMLU [Hendrycks et al., 2020] and MMLU-Pro [Wang et al., 2024b] evaluate broad subject knowledge, while GAIA [Mialon et al., 2023] and HLE [Phan et al., 2025] test long-context and high-difficulty reasoning. HumanEval [Chen et al., 2021] measures code generation accuracy, GPQA [Rein et al., 2024] targets graduate-level science, and GSM8k [Cobbe et al., 2021] focuses on arithmetic reasoning. Recent work such as DynaMath [Zou et al., 2024] evaluates VLMs' mathematical reasoning robustness.

LLMs in Engineering Domains. Recent studies have started to explore the applicability of LLMs to engineering contexts. For example, [Syed et al., 2024, Kevian et al., 2024, Guo and Zhao, 2025, Xu et al., 2025, Xiong et al., 2025, Eslaminia et al., 2024, Ogo and Koga, 2024] evaluate LLMs across engineering subfields using curated QA datasets. However, these efforts only focuses one specific domain or largely focus on factual recall rather than generative design capabilities. Several domain-specific studies examine LLM-assisted design workflows. For example, ControlAgent [Guo et al., 2024] integrates control theory solvers for automated controller design, while AnalogCoder [Lai et al., 2024] and SPICED [Chaudhuri et al., 2024] target analog circuit and SoC design using prompt engineering and retrieval-based techniques. Retrieval-augmented and programmatic strategies have also been explored to enhance LLM performance [Ghosh and Team, 2024, Alsaqer et al., 2024]. Other studies examine LLMs in mechanical design [Lu et al., 2024], cross-domain creativity [Jia et al., 2024], and computational engineering [Hamann et al., 2024, Xu et al., 2024, Majumder et al., 2024, Makatura et al., 2023]. Compared to prior work, ENGDESIGN spans multiple engineering domains and introduces a novel evaluation framework that combines generative outputs from LLMs with simulation-based evaluation to assess performance in realistic design settings.

## 5 Conclusion

In this work, we introduced ENGDESIGN, a comprehensive benchmark for rigorously evaluating large language models (LLMs) in realistic, multi-domain engineering design scenarios. ENGDESIGN emphasizes end-to-end design synthesis, constraint satisfaction, and simulation-based validation across diverse engineering disciplines. Our results show that ENGDESIGN poses substantial challenges: even the most capable frontier models achieve only modest performance. We envision ENGDESIGN as a foundation for future research at the intersection of language, reasoning, and engineering intelligence. By providing a standardized and reproducible evaluation testbed, we hope to accelerate progress toward the long-term goal of developing general-purpose AI engineers.

<sup>&</sup>lt;sup>3</sup>Additional failure cases and qualitative analyses are provided in Appendix E.

# Acknowledgment

Xingang Guo and Bin Hu are generously supported by the Amazon AICE award.

#### References

Chipdev platform. https://chipdev.io/, 2025.

Matlab and simulink examples. https://www.mathworks.com/academia/examples.html, 2025.

Josh Achiam, Steven Adler, Sandhini Agarwal, Lama Ahmad, Ilge Akkaya, Florencia Leoni Aleman, Diogo Almeida, Janko Altenschmidt, Sam Altman, Shyamal Anadkat, et al. Gpt-4 technical report. arXiv preprint arXiv:2303.08774, 2023.

Shadan Alsaqer, Sarah Alajmi, Imtiaz Ahmad, and Mohammad Alfailakawi. The potential of llms in hardware design. *Journal of Engineering Research*, 2024.

Antenna-Theory.com. The dipole antenna, 2011a. URL <a href="https://www.antenna-theory.com/antennas/dipole.php">https://www.antenna-theory.com/antennas/dipole.php</a>.

Antenna-Theory.com. Patch antennas, 2011b. URL https://www.antenna-theory.com/antennas/patches/patch4.php.

Anthropic. Claude 3.7 sonnet system card, a. URL https://assets.anthropic.com/m/785e231869ea8b3b/original/claude-3-7-sonnet-system-card.pdf.

Anthropic. Claude's extended thinking. https://www.anthropic.com/news/visible-extended-thinking, b.

Tamer Başar, Sean P. Meyn, and William R. Perkins. Lecture notes on control system theory and design. *arXiv* preprint arXiv:2007.01367, 2024.

SS Bhavikatti. Finite element analysis. New Age International, 2005.

David Blockley. Engineering: a very short introduction, volume 309. Oxford university press, 2012.

Bailey Brown, Nadim S Hmeidat, Xiu Jia, Jackson Wilt, Michael Roberts, Brett G Compton, and Natasha Vermaak. Experimental investigations of the effectiveness of simultaneous topology/orientation optimization via somp and principal stress directions. *Materials & Design*, 217:110647, 2022.

Tom Brown, Benjamin Mann, Nick Ryder, Melanie Subbiah, Jared D Kaplan, Prafulla Dhariwal, Arvind Neelakantan, Pranav Shyam, Girish Sastry, Amanda Askell, et al. Language models are few-shot learners. *Advances in neural information processing systems*, 33:1877–1901, 2020.

Business Wire. P-1 AI Comes Out of Stealth, Aims to Build Engineering AGI for Physical Systems. Press release, Business Wire, April 2025. URL https://www.businesswire.com/news/home/20250425073932/en/P-1-AI-Comes-Out-of-Stealth-Aims-to-Build-Engineering-AGI-for-Physical-Systems. San Francisco.

Jun Shern Chan, Neil Chowdhury, Oliver Jaffe, James Aung, Dane Sherburn, Evan Mays, Giulio Starace, Kevin Liu, Leon Maksin, Tejal Patwardhan, et al. Mle-bench: Evaluating machine learning agents on machine learning engineering. *arXiv preprint arXiv:2410.07095*, 2024.

Jayeeta Chaudhuri, Dhruv Thapar, Arjun Chaudhuri, Farshad Firouzi, and Krishnendu Chakrabarty. Spiced: Syntactical bug and trojan pattern identification in a/ms circuits using llm-enhanced detection. arXiv preprint arXiv:2408.16018, 2024.

Mark Chen, Jerry Tworek, Heewoo Jun, Qiming Yuan, Henrique Ponde De Oliveira Pinto, Jared Kaplan, Harri Edwards, Yuri Burda, Nicholas Joseph, Greg Brockman, et al. Evaluating large language models trained on code. *arXiv preprint arXiv:2107.03374*, 2021.

Wai-Fah Chen and JY Richard Liew. The civil engineering handbook. Crc Press, 2002.

Wai Kai Chen. The electrical engineering handbook. Elsevier, 2004.

Richard Y Chiang and Michael G Safonov. Matlab. Robust Control toolbox. User's guide (The Mathworks Inc., 1998), 1984.

- P.P. Chu. FPGA Prototyping by SystemVerilog Examples: Xilinx MicroBlaze MCS SoC Edition. Wiley, 2018. ISBN 9781119282662. URL https://books.google.com/books?id=CR5eDwAAQBAJ.

- Karl Cobbe, Vineet Kosaraju, Mohammad Bavarian, Mark Chen, Heewoo Jun, Lukasz Kaiser, Matthias Plappert, Jerry Tworek, Jacob Hilton, Reiichiro Nakano, et al. Training verifiers to solve math word problems. arXiv preprint arXiv:2110.14168, 2021.

- Tri Dao, Daniel Y. Fu, Stefano Ermon, Atri Rudra, and Christopher Ré. Flashattention: Fast and memory-efficient exact attention with io-awareness, 2022. URL https://arxiv.org/abs/2205.14135.

- Alejandro Dominguez-Garcia. Ece 486: Real-time operating systems and networks (spring 2025). https://courses.grainger.illinois.edu/ece486/sp2025/, 2025.

- Xinrun Du, Yifan Yao, Kaijing Ma, Bingli Wang, Tianyu Zheng, King Zhu, Minghao Liu, Yiming Liang, Xiaolong Jin, Zhenlin Wei, et al. Supergpqa: Scaling llm evaluation across 285 graduate disciplines. *arXiv* preprint arXiv:2502.14739, 2025.

- University of Illinois Urbana-Champaign ECE Department. Ece 385: Digital systems laboratory (spring 2025) course slides: Cpu control logic. https://courses.engr.illinois.edu/ece385, 2025a.

- University of Illinois Urbana-Champaign ECE Department. Ece 385: Digital systems laboratory (spring 2025) lab 5 specification. https://courses.engr.illinois.edu/ece385, 2025b.

- ECE Department, University of Illinois Urbana-Champaign. ECE 483: Analog IC Design (Spring 2025) Course Project Material: MP1. https://courses.engr.illinois.edu/ece483/sp2025/, 2025a.

- ECE Department, University of Illinois Urbana-Champaign. ECE 483: Analog IC Design (Spring 2025) Course Project Material: MP3. https://courses.engr.illinois.edu/ece483/sp2025/, 2025b.

- ECE Department, University of Illinois Urbana-Champaign. ECE 483: Analog IC Design (Spring 2025) Course Project Material: MP4. https://courses.engr.illinois.edu/ece483/sp2025/, 2025c.

- Ahmadreza Eslaminia, Adrian Jackson, Beitong Tian, Avi Stern, Hallie Gordon, Rajiv Malhotra, Klara Nahrstedt, and Chenhui Shao. Fdm-bench: A comprehensive benchmark for evaluating large language models in additive manufacturing tasks. *arXiv preprint arXiv:2412.09819*, 2024.

- FPGA4student. Seven-segment led display controller in verilog. https://www.fpga4student.com/2017/09/seven-segment-led-display-controller-verilog.html, 2017a.

- FPGA4student. Fpga verilog code for tetris game. https://www.fpga4student.com/2017/08/fpga-verilog-code-for-tetris-game.html, 2017b.

- Debi Prasad Ghosh and Design Automation Team. Retrieval-augmented generation in engineering design, 2024.

- Kai Goebel and Patrik Zips. Can Ilm-reasoning models replace classical planning? a benchmark study. *arXiv* preprint arXiv:2507.23589, 2025.

- Richard Gooch and Pekka Enberg. Overview of the linux virtual file system. https://docs.kernel.org/filesystems/vfs.html, 2005.

- Google DeepMind. Gemini: Our most capable model, updated with better thinking. https://blog.google/technology/google-deepmind/gemini-model-thinking-updates-march-2025/#gemini-2-5-thinking.

- Paul R Gray, Paul J Hurst, Stephen H Lewis, and Robert G Meyer. *Analysis and design of analog integrated circuits*. John Wiley & Sons, 2009.

- Karl-Heinrich Grote and Hamid Hefazi. Springer handbook of mechanical engineering. Springer Nature, 2021.

- Ce Guo and Tong Zhao. Resbench: Benchmarking llm-generated fpga designs with resource awareness. *arXiv* preprint arXiv:2503.08823, 2025.

- Daya Guo, Dejian Yang, Haowei Zhang, Junxiao Song, Ruoyu Zhang, Runxin Xu, Qihao Zhu, Shirong Ma, Peiyi Wang, Xiao Bi, et al. Deepseek-r1: Incentivizing reasoning capability in Ilms via reinforcement learning. arXiv preprint arXiv:2501.12948, 2025.

- Xingang Guo, Darioush Keivan, Usman Syed, Lianhui Qin, Huan Zhang, Geir Dullerud, Peter Seiler, and Bin Hu. Controlagent: Automating control system design via novel integration of llm agents and domain expertise. arXiv preprint arXiv:2410.19811, 2024.

- Hendrik F Hamann, Thomas Brunschwiler, Blazhe Gjorgiev, Leonardo SA Martins, Alban Puech, Anna Varbella, Jonas Weiss, Juan Bernabe-Moreno, Alexandre Blondin Massé, Seong Choi, et al. A perspective on foundation models for the electric power grid. arXiv preprint arXiv:2407.09434, 2024.

- Dan Hendrycks, Collin Burns, Steven Basart, Andy Zou, Mantas Mazeika, Dawn Song, and Jacob Steinhardt. Measuring massive multitask language understanding. *arXiv preprint arXiv:2009.03300*, 2020.

- J.L. Hennessy and D.A. Patterson. *Computer Architecture: A Quantitative Approach*. The Morgan Kaufmann Series in Computer Architecture and Design. Morgan Kaufmann, 2017. ISBN 9780128119068. URL <a href="https://books.google.com/books?id=cM8mDwAAQBAJ">https://books.google.com/books?id=cM8mDwAAQBAJ</a>.

- Joseph Howse and Joe Minichino. *Learning OpenCV 4 Computer Vision with Python 3*. Packt Publishing, 3rd edition, 2020. ISBN 978-1789531619.

- IEEE. Ieee standard for systemverilog—unified hardware design, specification, and verification language. *IEEE Std 1800-2017 (Revision of IEEE Std 1800-2012)*, pages 1–1315, 2018. doi: 10.1109/IEEESTD.2018. 8299595.

- Naman Jain, King Han, Alex Gu, Wen-Ding Li, Fanjia Yan, Tianjun Zhang, Sida Wang, Armando Solar-Lezama, Koushik Sen, and Ion Stoica. Livecodebench: Holistic and contamination free evaluation of large language models for code. *arXiv* preprint arXiv:2403.07974, 2024.

- Mengshuo Jia, Zeyu Cui, and Gabriela Hug. Enabling large language models to perform power system simulations with previously unseen tools: A case of daline. arXiv preprint arXiv:2406.17215, 2024.

- Zhe Jia, Blake Tillman, Marco Maggioni, and Daniele Paolo Scarpazza. Dissecting the graphcore ipu architecture via microbenchmarking, 2019. URL https://arxiv.org/abs/1912.03413.

- Norm Jouppi, George Kurian, Sheng Li, Peter Ma, Rahul Nagarajan, Lifeng Nai, Nishant Patil, Suvinay Subramanian, Andy Swing, Brian Towles, Clifford Young, Xiang Zhou, Zongwei Zhou, and David A Patterson. Tpu v4: An optically reconfigurable supercomputer for machine learning with hardware support for embeddings. In *Proceedings of the 50th Annual International Symposium on Computer Architecture*, ISCA '23, New York, NY, USA, 2023. Association for Computing Machinery. ISBN 9798400700958. doi: 10.1145/3579371.3589350. URL https://doi.org/10.1145/3579371.3589350.

- K R Kashwan, V Rajeshkumar, T Gunasekaran, and K R Shankar Kumar. Design and characterization of pin fed microstrip patch antennae. In 2011 Eighth International Conference on Fuzzy Systems and Knowledge Discovery (FSKD), volume 4, pages 2258–2262, 2011. doi: 10.1109/FSKD.2011.6020028.

- Darioush Kevian, Usman Syed, Xingang Guo, Aaron Havens, Geir Dullerud, Peter Seiler, Lianhui Qin, and Bin Hu. Capabilities of large language models in control engineering: A benchmark study on gpt-4, claude 3 opus, and gemini 1.0 ultra. arXiv preprint arXiv:2404.03647, 2024.

- Simon Knowles. Graphcore. In 2021 IEEE Hot Chips 33 Symposium (HCS), pages 1–25, 2021. doi: 10.1109/HCS52781.2021.9567075.

- Bram Lagerweij. Topopt: Topology optimization in python. https://github.com/AJJLagerweij/topopt, 2024.

- Yao Lai, Sungyoung Lee, Guojin Chen, Souradip Poddar, Mengkang Hu, David Z Pan, and Ping Luo. Analog-coder: Analog circuit design via training-free code generation. arXiv preprint arXiv:2405.14918, 2024.

- Yao Lai, Sungyoung Lee, Guojin Chen, Souradip Poddar, Mengkang Hu, David Z Pan, and Ping Luo. Analog-coder: Analog circuit design via training-free code generation. In *Proceedings of the AAAI Conference on Artificial Intelligence*, volume 39, pages 379–387, 2025a.

- Yao Lai, Souradip Poddar, Sungyoung Lee, Guojin Chen, Mengkang Hu, Bei Yu, Ping Luo, and David Z Pan. Analogcoder-pro: Unifying analog circuit generation and optimization via multi-modal llms. *arXiv preprint* arXiv:2508.02518, 2025b.

- Eugene Lavretsky and Kevin A. Wise. *Frequency Domain Analysis*, pages 103–176. Springer International Publishing, Cham, 2024. ISBN 978-3-031-38314-4. doi: 10.1007/978-3-031-38314-4\_3. URL https://doi.org/10.1007/978-3-031-38314-4\_3.

- Junghee Lee, Youngjae Kim, Galen M Shipman, Sarp Oral, and Jongman Kim. Preemptible i/o scheduling of garbage collection for solid state drives. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 32(2):247–260, 2013.

- Kirill Levchenko. Virtual memory. Lecture slides, ECE391 Course Materials, University of Illinois Urbana–Champaign, Fall 2024.

- Kirill Levchenko. File system. Lecture slides, ECE391 Course Materials, University of Illinois Urbana–Champaign, Spring 2025.

- Ming Li, Jike Zhong, Tianle Chen, Yuxiang Lai, and Konstantinos Psounis. Eee-bench: A comprehensive multimodal electrical and electronics engineering benchmark. *arXiv* preprint arXiv:2411.01492, 2024.

- Shangyu Li, Juyong Jiang, Tiancheng Zhao, and Jiasi Shen. Osvbench: Benchmarking Ilms on specification generation tasks for operating system verification. *arXiv* preprint arXiv:2504.20964, 2025a.

- Yinsheng Li, Zhen Dong, and Yi Shao. Drafterbench: Benchmarking large language models for tasks automation in civil engineering. *arXiv preprint arXiv:2507.11527*, 2025b.

- Chen Liang, Zhaoqi Huang, Haofen Wang, Fu Chai, Chunying Yu, Huanhuan Wei, Zhengjie Liu, Yanpeng Li, Hongjun Wang, Ruifeng Luo, et al. Aecbench: A hierarchical benchmark for knowledge evaluation of large language models in the aec field. *arXiv preprint arXiv:2509.18776*, 2025.

- Sean Lie. Multi-million core, multi-wafer ai cluster. In 2021 IEEE Hot Chips 33 Symposium (HCS), pages 1–41, 2021. doi: 10.1109/HCS52781.2021.9567153.

- Aixin Liu, Bei Feng, Bing Xue, Bingxuan Wang, Bochao Wu, Chengda Lu, Chenggang Zhao, Chengqi Deng, Chenyu Zhang, Chong Ruan, et al. Deepseek-v3 technical report. *arXiv preprint arXiv:2412.19437*, 2024a.

- Jason Liu and Contributors. Instructor: A library for structured outputs from large language models, 3 2024. URL https://github.com/instructor-ai/instructor.

- Mingjie Liu, Nathaniel Pinckney, Brucek Khailany, and Haoxing Ren. Verilogeval: Evaluating large language models for verilog code generation. In 2023 IEEE/ACM International Conference on Computer Aided Design (ICCAD), pages 1–8. IEEE, 2023.

- Yiqi Liu, Yuqi Xue, Yu Cheng, Lingxiao Ma, Ziming Miao, Jilong Xue, and Jian Huang. Scaling deep learning computation over the inter-core connected intelligence processor with t10. In *Proceedings of the ACM SIGOPS 30th Symposium on Operating Systems Principles*, SOSP '24, page 505–521. ACM, November 2024b. doi: 10.1145/3694715.3695955. URL http://dx.doi.org/10.1145/3694715.3695955.

- Jiaxing Lu, Heran Li, Fangwei Ning, Yixuan Wang, Xinze Li, and Yan Shi. Constructing mechanical design agent based on large language models. *arXiv preprint arXiv:2408.02087*, 2024.

- Subir Majumder, Lin Dong, Fatemeh Doudi, Yuting Cai, Chao Tian, Dileep Kalathil, Kevin Ding, Anupam A Thatte, Na Li, and Le Xie. Exploring the capabilities and limitations of large language models in the electric energy sector. *Joule*, 8(6):1544–1549, 2024.

- Liane Makatura, Michael Foshey, Bohan Wang, Felix HähnLein, Pingchuan Ma, Bolei Deng, Megan Tjandrasuwita, Andrew Spielberg, Crystal Elaine Owens, Peter Yichen Chen, et al. How can large language models help humans in design and manufacturing? *arXiv preprint arXiv:2307.14377*, 2023.

- François Mazé and Faez Ahmed. Diffusion models beat gans on topology optimization, 2022a. URL https://arxiv.org/abs/2208.09591.

- François Mazé and Faez Ahmed. Topodiff project page. https://decode.mit.edu/projects/topodiff/, 2022b.

- Grégoire Mialon, Clémentine Fourrier, Thomas Wolf, Yann LeCun, and Thomas Scialom. Gaia: a benchmark for general ai assistants. In *The Twelfth International Conference on Learning Representations*, 2023.

- Bo Ni and Markus J Buehler. Mechagents: Large language model multi-agent collaborations can solve mechanics problems, generate new data, and integrate knowledge. *Extreme Mechanics Letters*, 67:102131, 2024.

- Jean P. Nicolle. Pong game. https://www.fpga4fun.com/PongGame.html.

- Thomas Norrie, Nishant Patil, Doe Hyun Yoon, George Kurian, Sheng Li, James Laudon, Cliff Young, Norman Jouppi, and David Patterson. The design process for google's training chips: Tpuv2 and tpuv3. *IEEE Micro*, 41(2):56–63, 2021. doi: 10.1109/MM.2021.3058217.

- Itsuki Ogo and Masanobu Koga. Can chatgpt pass modern control theory exam? In 2024 24th International Conference on Control, Automation and Systems (ICCAS), pages 1287–1292. IEEE, 2024.

- OpenAI. Openai o3 and o4-mini system card. URL https://cdn.openai.com/pdf/ 2221c875-02dc-4789-800b-e7758f3722c1/o3-and-o4-mini-system-card.pdf.

- Saswata Paul, Elkin Cruz, Airin Dutta, Ankita Bhaumik, Erik Blasch, Gul Agha, Stacy Patterson, Fotis Kopsaftopoulos, and Carlos Varela. Formal verification of safety-critical aerospace systems. *IEEE Aerospace* and Electronic Systems Magazine, 38(5):72–88, 2023.

- Long Phan, Alice Gatti, Ziwen Han, Nathaniel Li, Josephina Hu, Hugh Zhang, Chen Bo Calvin Zhang, Mohamed Shaaban, John Ling, Sean Shi, et al. Humanity's last exam. *arXiv preprint arXiv:2501.14249*, 2025.

- Raghu Prabhakar and Sumti Jairath. Sambanova sn10 rdu:accelerating software 2.0 with dataflow. In 2021 IEEE Hot Chips 33 Symposium (HCS), pages 1–37, 2021. doi: 10.1109/HCS52781.2021.9567250.

- Pengrui Quan, Xiaomin Ouyang, Jeya Vikranth Jeyakumar, Ziqi Wang, Yang Xing, and Mani Srivastava. Sensorbench: Benchmarking Ilms in coding-based sensor processing. In *Proceedings of the 26th International Workshop on Mobile Computing Systems and Applications*, pages 25–30, 2025.

- Saeed Rashidi, William Won, Sudarshan Srinivasan, Srinivas Sridharan, and Tushar Krishna. Themis: a network bandwidth-aware collective scheduling policy for distributed training of dl models. In *Proceedings of the 49th Annual International Symposium on Computer Architecture*, ISCA '22, page 581–596. ACM, June 2022. doi: 10.1145/3470496.3527382. URL http://dx.doi.org/10.1145/3470496.3527382.

- David Rein, Betty Li Hou, Asa Cooper Stickland, Jackson Petty, Richard Yuanzhe Pang, Julien Dirani, Julian Michael, and Samuel R Bowman. Gpqa: A graduate-level google-proof q&a benchmark. In First Conference on Language Modeling, 2024.

- RISC-V Privileged Horizontal Committee. The risc-v instruction set manual volume ii: Privileged architecture. https://drive.google.com/file/d/17GeetSnT5wW3xNuAHI95-SI1gPGd5sJ\_/view, 2024.

- Gordon W Roberts. Spice. Oxford University Press, Inc., 1996.

- M. Safonov, A. Laub, and G. Hartmann. Feedback properties of multivariable systems: The role and use of the return difference matrix. *IEEE Transactions on Automatic Control*, 26(1):47–65, 1981. doi: 10.1109/TAC. 1981.1102566.

- S. Salapaka, A. Sebastian, J. P. Cleveland, and M. V. Salapaka. High bandwidth nano-positioner: A robust control approach. *Review of Scientific Instruments*, 73(9):3232–3241, 09 2002. ISSN 0034-6748. doi: 10.1063/1.1499533. URL https://doi.org/10.1063/1.1499533.

- Peter Seiler and Julian Theis. An Introduction to Classical Control and Loopshaping.

- Mohammad Shoeybi, Mostofa Patwary, Raul Puri, Patrick LeGresley, Jared Casper, and Bryan Catanzaro. Megatron-lm: Training multi-billion parameter language models using model parallelism, 2020. URL https://arxiv.org/abs/1909.08053.

- Lejla Skelic, Yan Xu, Matthew Cox, Wenjie Lu, Tao Yu, and Ruonan Han. Circuit: A benchmark for circuit interpretation and reasoning capabilities of llms. *arXiv preprint arXiv:2502.07980*, 2025.

- Xavier Soria, Edgar Riba, and Angel Sappa. Dense extreme inception network: Towards a robust cnn model for edge detection. In *The IEEE Winter Conference on Applications of Computer Vision (WACV '20)*, 2020.

- Kun Wu Steven S. Lumetta. Ece 508: Manycore parallel algorithms (spring 2023) lecture 4. https://lumetta.web.engr.illinois.edu/508/slides/lecture4.pdf, 2023.

- David Strassera. Openlapsim. https://github.com/dstrassera/OpenLapSim, 2021.

- Kenneth Sutton and Randolph A. Graves. A general stagnation-point convective heating equation for arbitrary gas mixtures. 1971. URL https://api.semanticscholar.org/CorpusID:52257986.

- Usman Syed, Ethan Light, Xingang Guo, Huan Zhang, Lianhui Qin, Yanfeng Ouyang, and Bin Hu. Benchmarking the capabilities of large language models in transportation system engineering: Accuracy, consistency, and reasoning behaviors. *arXiv* preprint arXiv:2408.08302, 2024.

- Gemini Team, Rohan Anil, Sebastian Borgeaud, Jean-Baptiste Alayrac, Jiahui Yu, Radu Soricut, Johan Schalkwyk, Andrew M Dai, Anja Hauth, Katie Millican, et al. Gemini: a family of highly capable multimodal models. *arXiv preprint arXiv:2312.11805*, 2023.

- Chee-Wooi Ten and Yunhe Hou. Modern power system analysis. CRC Press, 2024.

- Tetris Wiki contributors. Tetris guideline. https://tetris.fandom.com/wiki/Tetris\_Guideline.

- The JAX Authors. Matrix multiplication. https://docs.jax.dev/en/latest/pallas/tpu/matmul.html, 2024.

- Michael S Tsirkin and Cornelia Huck. Virtual i/o device (virtio) version 1.1. OASIS Committee, 2022.

- University of Michigan. Control tutorials for matlab and simulink pid controller design. https://ctms.engin.umich.edu/CTMS/index.php?example=Introduction&section=ControlPID.

- Nicolas Vasilache, Oleksandr Zinenko, Theodoros Theodoridis, Priya Goyal, Zachary DeVito, William S. Moses, Sven Verdoolaege, Andrew Adams, and Albert Cohen. Tensor comprehensions: Framework-agnostic high-performance machine learning abstractions, 2018. URL https://arxiv.org/abs/1802.04730.

- Gwok-Waa Wan, Shengchu Su, Ruihu Wang, Qixiang Chen, Sam-Zaak Wong, Mengnv Xing, Hefei Feng, Yubo Wang, Yinan Zhu, Jingyi Zhang, et al. Fixme: Towards end-to-end benchmarking of llm-aided design verification. *arXiv preprint arXiv:2507.04276*, 2025.

- Xi Wang, Gwok-Waa Wan, Sam-Zaak Wong, Layton Zhang, Tianyang Liu, Qi Tian, and Jianmin Ye. Chatcpu: An agile cpu design and verification platform with llm. In *Proceedings of the 61st ACM/IEEE Design Automation Conference*, pages 1–6, 2024a.

- Yubo Wang, Xueguang Ma, Ge Zhang, Yuansheng Ni, Abhranil Chandra, Shiguang Guo, Weiming Ren, Aaran Arulraj, Xuan He, Ziyan Jiang, et al. Mmlu-pro: A more robust and challenging multi-task language understanding benchmark. In *The Thirty-eight Conference on Neural Information Processing Systems Datasets and Benchmarks Track*, 2024b.

- Andrew Waterman, Yunsup Lee, Rimas Avizienis, David A Patterson, and Krste Asanovic. The risc-v instruction set manual volume ii: Privileged architecture version 1.7. *EECS Department, University of California, Berkeley, Tech. Rep. UCB/EECS-2016-129*, 2016.

- Jason Wei, Xuezhi Wang, Dale Schuurmans, Maarten Bosma, Fei Xia, Ed Chi, Quoc V Le, Denny Zhou, et al. Chain-of-thought prompting elicits reasoning in large language models. Advances in neural information processing systems, 35:24824–24837, 2022.

- Huan Weng, Bill Hunt, Jarvis Schultz, and Mikhail Todes. Modern robotics: Mechanics, planning, and control code library. https://github.com/NxRLab/ModernRobotics, 2018.

- Wikipedia contributors. Clustered file system. Wikipedia, The Free Encyclopedia. https://en.wikipedia.org/wiki/Clustered\_file\_system, a.

- Wikipedia contributors. Round-robin scheduling. Wikipedia, The Free Encyclopedia. https://en.wikipedia.org/wiki/Round-robin\_scheduling, b.

- Yuyang Wu, Yifei Wang, Ziyu Ye, Tianqi Du, Stefanie Jegelka, and Yisen Wang. When more is less: Understanding chain-of-thought length in llms. *arXiv preprint arXiv:2502.07266*, 2025.

- Ruoxin Xiong, Yanyu Wang, Suat Gunhan, Yimin Zhu, and Charles Berryman. Can ai master construction management (cm)? benchmarking state-of-the-art large language models on cm certification exams. arXiv preprint arXiv:2504.08779, 2025.

- Boyan Xu, Liang Wen, Zihao Li, Yuxing Yang, Guanlan Wu, Xiongpeng Tang, Yu Li, Zihao Wu, Qingxian Su, Xueqing Shi, et al. Unlocking the potential: Benchmarking large language models in water engineering and research. *arXiv preprint arXiv:2407.21045*, 2024.

- Boyan Xu, Zihao Li, Yuxin Yang, Guanlan Wu, Chengzhi Wang, Xiongpeng Tang, Yu Li, Zihao Wu, Qingxian Su, Xueqing Shi, et al. Evaluating and advancing large language models for water knowledge tasks in engineering and research. *Environmental Science & Technology Letters*, 12(3):289–296, 2025.

- Yuqi Xue, Yiqi Liu, Lifeng Nai, and Jian Huang. V10: Hardware-assisted npu multi-tenancy for improved resource utilization and fairness. In *Proceedings of the 50th Annual International Symposium on Computer Architecture*, ISCA '23, New York, NY, USA, 2023. Association for Computing Machinery. ISBN 9798400700958. doi: 10.1145/3579371.3589059. URL https://doi.org/10.1145/3579371.3589059.

- Yuqi Xue, Yiqi Liu, Lifeng Nai, and Jian Huang. Hardware-assisted virtualization of neural processing units for cloud platforms. In 2024 57th IEEE/ACM International Symposium on Microarchitecture (MICRO), pages 1–16, 2024. doi: 10.1109/MICRO61859.2024.00011.

- Sheng Yin, Xianghe Pang, Yuanzhuo Ding, Menglan Chen, Yutong Bi, Yichen Xiong, Wenhao Huang, Zhen Xiang, Jing Shao, and Siheng Chen. Safeagentbench: A benchmark for safe task planning of embodied llm agents. arXiv preprint arXiv:2412.13178, 2024.

- Lianmin Zheng, Chengfan Jia, Minmin Sun, Zhao Wu, Cody Hao Yu, Ameer Haj-Ali, Yida Wang, Jun Yang, Danyang Zhuo, Koushik Sen, Joseph E. Gonzalez, and Ion Stoica. Ansor: Generating high-performance tensor programs for deep learning, 2023. URL https://arxiv.org/abs/2006.06762.

- Corey Snyder Zhi-Pei Liang. Ece 310: Digital signal processing (spring 2025). https://courses.grainger.illinois.edu/ece310/sp2025/, 2025.

- Denny Zhou, Nathanael Schärli, Le Hou, Jason Wei, Nathan Scales, Xuezhi Wang, Dale Schuurmans, Claire Cui, Olivier Bousquet, Quoc Le, et al. Least-to-most prompting enables complex reasoning in large language models. arXiv preprint arXiv:2205.10625, 2022.

- Hongyu Zhu, Ruofan Wu, Yijia Diao, Shanbin Ke, Haoyu Li, Chen Zhang, Jilong Xue, Lingxiao Ma, Yuqing Xia, Wei Cui, Fan Yang, Mao Yang, Lidong Zhou, Asaf Cidon, and Gennady Pekhimenko. ROLLER: Fast and efficient tensor compilation for deep learning. In *16th USENIX Symposium on Operating Systems Design and Implementation (OSDI 22)*, pages 233–248, Carlsbad, CA, July 2022. USENIX Association. ISBN 978-1-939133-28-1. URL https://www.usenix.org/conference/osdi22/presentation/zhu.

- Yuqi Zhu, Ge Li, Xue Jiang, Jia Li, Hong Mei, Zhi Jin, and Yihong Dong. Uncertainty-guided chain-of-thought for code generation with llms. *arXiv preprint arXiv:2503.15341*, 2025.

- Chengke Zou, Xingang Guo, Rui Yang, Junyu Zhang, Bin Hu, and Huan Zhang. Dynamath: A dynamic visual benchmark for evaluating mathematical reasoning robustness of vision language models. *arXiv preprint arXiv:2411.00836*, 2024.

- Yazhou Zu, Alireza Ghaffarkhah, Hoang-Vu Dang, Brian Towles, Steven Hand, Safeen Huda, Adekunle Bello, Alexander Kolbasov, Arash Rezaei, Dayou Du, Steve Lacy, Hang Wang, Aaron Wisner, Chris Lewis, and Henri Bahini. Resiliency at scale: Managing Google's TPUv4 machine learning supercomputer. In 21st USENIX Symposium on Networked Systems Design and Implementation (NSDI 24), pages 761–774, Santa Clara, CA, April 2024. USENIX Association. ISBN 978-1-939133-39-7. URL https://www.usenix.org/conference/nsdi24/presentation/zu.

# **NeurIPS Paper Checklist**

The checklist is designed to encourage best practices for responsible machine learning research, addressing issues of reproducibility, transparency, research ethics, and societal impact. Do not remove the checklist: **The papers not including the checklist will be desk rejected.** The checklist should follow the references and follow the (optional) supplemental material. The checklist does NOT count towards the page limit.

Please read the checklist guidelines carefully for information on how to answer these questions. For each question in the checklist:

- You should answer [Yes], [No], or [NA].

- [NA] means either that the question is Not Applicable for that particular paper or the relevant information is Not Available.

- Please provide a short (1–2 sentence) justification right after your answer (even for NA).

The checklist answers are an integral part of your paper submission. They are visible to the reviewers, area chairs, senior area chairs, and ethics reviewers. You will be asked to also include it (after eventual revisions) with the final version of your paper, and its final version will be published with the paper.

The reviewers of your paper will be asked to use the checklist as one of the factors in their evaluation. While "[Yes]" is generally preferable to "[No]", it is perfectly acceptable to answer "[No]" provided a proper justification is given (e.g., "error bars are not reported because it would be too computationally expensive" or "we were unable to find the license for the dataset we used"). In general, answering "[No]" or "[NA]" is not grounds for rejection. While the questions are phrased in a binary way, we acknowledge that the true answer is often more nuanced, so please just use your best judgment and write a justification to elaborate. All supporting evidence can appear either in the main paper or the supplemental material, provided in appendix. If you answer [Yes] to a question, in the justification please point to the section(s) where related material for the question can be found.

## IMPORTANT, please:

- Delete this instruction block, but keep the section heading "NeurIPS Paper Checklist",

- Keep the checklist subsection headings, questions/answers and guidelines below.

- Do not modify the questions and only use the provided macros for your answers.

#### 1. Claims

Question: Do the main claims made in the abstract and introduction accurately reflect the paper's contributions and scope?

Answer: [Yes]

Justification: We introduced ENGDESIGN benchmark in this work to benchmark the engineering design capabilities of current LLMs. The dataset details have been discussed in Section 2, and our experimental results are included in Section 3.

## Guidelines:

- The answer NA means that the abstract and introduction do not include the claims made in the paper.

- The abstract and/or introduction should clearly state the claims made, including the contributions made in the paper and important assumptions and limitations. A No or NA answer to this question will not be perceived well by the reviewers.

- The claims made should match theoretical and experimental results, and reflect how much the results can be expected to generalize to other settings.

- It is fine to include aspirational goals as motivation as long as it is clear that these goals

are not attained by the paper.

#### 2. Limitations

Question: Does the paper discuss the limitations of the work performed by the authors?

Answer: [Yes]

Justification: We have discussed the limitations of our work in Appendix A. Guidelines:

- The answer NA means that the paper has no limitation while the answer No means that the paper has limitations, but those are not discussed in the paper.

- The authors are encouraged to create a separate "Limitations" section in their paper.

- The paper should point out any strong assumptions and how robust the results are to violations of these assumptions (e.g., independence assumptions, noiseless settings, model well-specification, asymptotic approximations only holding locally). The authors should reflect on how these assumptions might be violated in practice and what the implications would be.

- The authors should reflect on the scope of the claims made, e.g., if the approach was only tested on a few datasets or with a few runs. In general, empirical results often depend on implicit assumptions, which should be articulated.

- The authors should reflect on the factors that influence the performance of the approach. For example, a facial recognition algorithm may perform poorly when image resolution is low or images are taken in low lighting. Or a speech-to-text system might not be used reliably to provide closed captions for online lectures because it fails to handle technical jargon.

- The authors should discuss the computational efficiency of the proposed algorithms and how they scale with dataset size.

- If applicable, the authors should discuss possible limitations of their approach to address problems of privacy and fairness.

- While the authors might fear that complete honesty about limitations might be used by reviewers as grounds for rejection, a worse outcome might be that reviewers discover limitations that aren't acknowledged in the paper. The authors should use their best judgment and recognize that individual actions in favor of transparency play an important role in developing norms that preserve the integrity of the community. Reviewers will be specifically instructed to not penalize honesty concerning limitations.

## 3. Theory assumptions and proofs

Question: For each theoretical result, does the paper provide the full set of assumptions and a complete (and correct) proof?

Answer: [NA]

Justification: Our paper does not include theoretical results.

#### Guidelines:

- The answer NA means that the paper does not include theoretical results.

- All the theorems, formulas, and proofs in the paper should be numbered and crossreferenced.

- All assumptions should be clearly stated or referenced in the statement of any theorems.

- The proofs can either appear in the main paper or the supplemental material, but if they appear in the supplemental material, the authors are encouraged to provide a short proof sketch to provide intuition.

- Inversely, any informal proof provided in the core of the paper should be complemented by formal proofs provided in appendix or supplemental material.

- Theorems and Lemmas that the proof relies upon should be properly referenced.

# 4. Experimental result reproducibility

Question: Does the paper fully disclose all the information needed to reproduce the main experimental results of the paper to the extent that it affects the main claims and/or conclusions of the paper (regardless of whether the code and data are provided or not)?

Answer: [Yes]

Justification: We have open-sourced our dataset and evaluation pipeline to reproduce our work.

- The answer NA means that the paper does not include experiments.

- If the paper includes experiments, a No answer to this question will not be perceived well by the reviewers: Making the paper reproducible is important, regardless of whether the code and data are provided or not.

- If the contribution is a dataset and/or model, the authors should describe the steps taken to make their results reproducible or verifiable.

- Depending on the contribution, reproducibility can be accomplished in various ways. For example, if the contribution is a novel architecture, describing the architecture fully might suffice, or if the contribution is a specific model and empirical evaluation, it may be necessary to either make it possible for others to replicate the model with the same dataset, or provide access to the model. In general, releasing code and data is often one good way to accomplish this, but reproducibility can also be provided via detailed instructions for how to replicate the results, access to a hosted model (e.g., in the case of a large language model), releasing of a model checkpoint, or other means that are appropriate to the research performed.

- While NeurIPS does not require releasing code, the conference does require all submissions to provide some reasonable avenue for reproducibility, which may depend on the nature of the contribution. For example

- (a) If the contribution is primarily a new algorithm, the paper should make it clear how to reproduce that algorithm.

- (b) If the contribution is primarily a new model architecture, the paper should describe the architecture clearly and fully.

- (c) If the contribution is a new model (e.g., a large language model), then there should either be a way to access this model for reproducing the results or a way to reproduce the model (e.g., with an open-source dataset or instructions for how to construct the dataset).

- (d) We recognize that reproducibility may be tricky in some cases, in which case authors are welcome to describe the particular way they provide for reproducibility. In the case of closed-source models, it may be that access to the model is limited in some way (e.g., to registered users), but it should be possible for other researchers to have some path to reproducing or verifying the results.

# 5. Open access to data and code

Question: Does the paper provide open access to the data and code, with sufficient instructions to faithfully reproduce the main experimental results, as described in supplemental material?

Answer: [Yes]

Justification: We have provided open access to the benchmark data including all the task prompt, domains, and topics. In addition, we have provided a github repo contains all the evaluations logs and evaluation pipeline for each task of ENGDESIGN.

- The answer NA means that paper does not include experiments requiring code.

- Please see the NeurIPS code and data submission guidelines (https://nips.cc/public/guides/CodeSubmissionPolicy) for more details.

- While we encourage the release of code and data, we understand that this might not be possible, so "No" is an acceptable answer. Papers cannot be rejected simply for not including code, unless this is central to the contribution (e.g., for a new open-source benchmark).

- The instructions should contain the exact command and environment needed to run to reproduce the results. See the NeurIPS code and data submission guidelines (https://nips.cc/public/guides/CodeSubmissionPolicy) for more details.

- The authors should provide instructions on data access and preparation, including how to access the raw data, preprocessed data, intermediate data, and generated data, etc.

- The authors should provide scripts to reproduce all experimental results for the new proposed method and baselines. If only a subset of experiments are reproducible, they should state which ones are omitted from the script and why.

- At submission time, to preserve anonymity, the authors should release anonymized versions (if applicable).

- Providing as much information as possible in supplemental material (appended to the paper) is recommended, but including URLs to data and code is permitted.

#### 6. Experimental setting/details

Question: Does the paper specify all the training and test details (e.g., data splits, hyper-parameters, how they were chosen, type of optimizer, etc.) necessary to understand the results?

Answer: [Yes]

Justification: We can explained our experimental setup in detail in Appendix D.1.

#### Guidelines:

- The answer NA means that the paper does not include experiments.

- The experimental setting should be presented in the core of the paper to a level of detail that is necessary to appreciate the results and make sense of them.

- The full details can be provided either with the code, in appendix, or as supplemental

material.

### 7. Experiment statistical significance

Question: Does the paper report error bars suitably and correctly defined or other appropriate information about the statistical significance of the experiments?

Answer: [Yes]

Justification: We report error bars in Table 11 and Table 12, which presents the detailed evaluation results. Specifically, during evaluation, we ran each task three independent trials to compute the mean and standard deviation results.

#### Guidelines:

- The answer NA means that the paper does not include experiments.

- The authors should answer "Yes" if the results are accompanied by error bars, confidence intervals, or statistical significance tests, at least for the experiments that support the main claims of the paper.

- The factors of variability that the error bars are capturing should be clearly stated (for example, train/test split, initialization, random drawing of some parameter, or overall run with given experimental conditions).

- The method for calculating the error bars should be explained (closed form formula, call to a library function, bootstrap, etc.)

- The assumptions made should be given (e.g., Normally distributed errors).

- It should be clear whether the error bar is the standard deviation or the standard error of the mean.

- It is OK to report 1-sigma error bars, but one should state it. The authors should preferably report a 2-sigma error bar than state that they have a 96% CI, if the hypothesis of Normality of errors is not verified.

- For asymmetric distributions, the authors should be careful not to show in tables or figures symmetric error bars that would yield results that are out of range (e.g. negative error rates).

- If error bars are reported in tables or plots, The authors should explain in the text how they were calculated and reference the corresponding figures or tables in the text.

#### 8. Experiments compute resources

Question: For each experiment, does the paper provide sufficient information on the computer resources (type of compute workers, memory, time of execution) needed to reproduce the experiments?

Answer: [Yes]

Justification: We have discussed the required compute resources in Appendix D.1.

- The answer NA means that the paper does not include experiments.

- The paper should indicate the type of compute workers CPU or GPU, internal cluster, or cloud provider, including relevant memory and storage.

- The paper should provide the amount of compute required for each of the individual experimental runs as well as estimate the total compute.

- The paper should disclose whether the full research project required more compute than the experiments reported in the paper (e.g., preliminary or failed experiments that didn't make it into the paper).

#### 9. Code of ethics

Question: Does the research conducted in the paper conform, in every respect, with the NeurIPS Code of Ethics <a href="https://neurips.cc/public/EthicsGuidelines">https://neurips.cc/public/EthicsGuidelines</a>?

Answer: [Yes]

Justification: This work adheres to the NeurIPS Code of Ethics. All experiments were conducted responsibly, without harm to individuals or groups, and without the use of sensitive or personally identifiable data. We also carefully considered the potential societal impact of our methods and reported both the limitations and potential risks in the paper.

## Guidelines:

- The answer NA means that the authors have not reviewed the NeurIPS Code of Ethics.

- If the authors answer No, they should explain the special circumstances that require a

deviation from the Code of Ethics.