# FALCON: An ML Framework for Fully Automated Layout-Constrained Analog Circuit Design

#### **Anonymous Author(s)**

Affiliation Address email

### **Abstract**

Designing analog circuits from performance specifications is a complex, multistage process encompassing topology selection, parameter inference, and layout feasibility. We introduce FALCON, a unified machine learning framework that enables fully automated, specification-driven analog circuit synthesis through topology selection and layout-constrained optimization. Given a target performance, FALCON first selects an appropriate circuit topology using a performance-driven classifier guided by human design heuristics. Next, it employs a custom, edgecentric graph neural network trained to map circuit topology and parameters to performance, enabling gradient-based parameter inference through the learned forward model. This inference is guided by a differentiable layout cost, derived from analytical equations capturing parasitic and frequency-dependent effects, and constrained by design rules. We train and evaluate FALCON on a large-scale custom dataset of 1M analog mm-wave circuits, generated and simulated using Cadence Spectre across 20 expert-designed topologies. Through this evaluation, FALCON demonstrates >99% accuracy in topology inference, <10% relative error in performance prediction, and efficient layout-aware design that completes in under 1 second per instance. Together, these results position FALCON as a practical and extensible foundation model for end-to-end analog circuit design automation.

## 19 1 Introduction

2

3

5

6

7

8

10

11

12

13

14

15

16

17

18

Analog radio frequency (RF) and millimeter-wave (mm-wave) circuits are central to modern electron-20 ics, powering applications in signal processing [1], wireless communication [2], sensing [3], radar [4], 21 and wireless power transfer [5]. Yet their design remains largely manual and heuristic-driven [6–8], 22 hindered by a vast continuous design space, tightly coupled trade-offs among gain, noise, bandwidth, 23 and power, and strong layout-dependent interactions. As demand for high-performance custom 24 blocks grows, this slow, expert-dependent cycle has become a bottleneck. While ML has transformed 25 digital design automation, analog efforts remain fragmented: most focus on isolated tasks such as topology generation or device sizing [9, 10], often assuming fixed topologies [11–14], relying on 27 non-scalable black-box optimization [15], or predicting performance without supporting inverse 28 design [16]. Layout is usually treated as post-processing [17], and benchmarks often rely on sym-29 bolic or synthetic data [18], limiting realism. Consequently, no current ML pipeline achieves fully 30 generalizable, layout-aware, end-to-end analog circuit design. 31

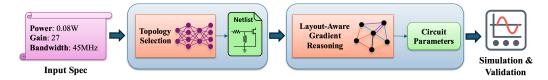

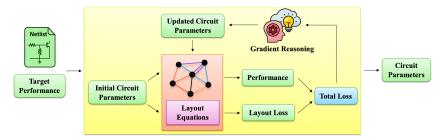

We propose FALCON (Fully Automated Layout-Constrained analOg circuit desigN), a scalable ML framework for end-to-end analog and RF design. Trained on over one million Cadence-simulated circuits, FALCON integrates three stages (Figure 1): (1) a multilayer perceptron (MLP) selects the topology from target specifications; (2) a graph neural network (GNN) maps topology and parameters to performance on native netlist graphs; and (3) gradient-based optimization over the GNN recovers

Figure 1: Our AI-based circuit design pipeline. Given a target performance specification, FALCON first selects a suitable topology, then generates design parameters through layout-aware gradient-based reasoning with GNN model. Then, the synthesized circuit is validated using Cadence simulations.

parameters that satisfy targets under a differentiable layout-aware loss. The GNN generalizes to unseen topologies with optional fine-tuning, enabling inverse design across circuit families. By embedding layout constraints directly in optimization, FALCON unifies schematic and physical considerations within a single differentiable framework.<sup>1</sup>

- 41 Our main contributions are as follows:

- We construct a large-scale analog/RF circuit dataset comprising over one million Cadencesimulated datapoints across 20 expert-designed topologies and five circuit types.

- We introduce a native netlist-to-graph representation that preserves both structural and parametric fidelity, enabling accurate learning over physical circuit topologies.

- We develop a modular ML framework for end-to-end inverse design, incorporating

performance-driven topology selection and layout-aware gradient-based optimization, with

a differentiable loss that enforces area constraints, design-rule compliance, and frequencydependent modeling of passive components.

- We design a generalizable GNN capable of accurate performance prediction and parameter inference across both seen and unseen topologies, with optional fine-tuning.

## 2 Related Work

While recent ML-based approaches have advanced analog and RF circuit design, they typically target isolated stages of the design flow—such as topology generation, parameter sizing, or schematic-level performance prediction—without supporting unified, end-to-end synthesis. FALCON bridges this gap by jointly addressing aforementioned stages within a single framework.

**Topology generation** methods aim to select or synthesize candidate circuit structures [9, 19, 20], often using discrete optimization or generative models to explore the circuit graph space. However, these approaches typically target low-frequency or simplified designs [9] and may produce physically invalid or non-manufacturable topologies. In contrast, FALCON leverages a curated set of netlists, ensuring manufacturable validity and eliminating the need to rediscover fundamental circuit structures.

Parameter sizing and performance prediction have been explored through various learning paradigms. Reinforcement learning [10, 21] and Bayesian optimization [15, 22] optimize parameters via trial-and-error, often requiring large simulation budgets. Supervised learning methods [23, 24, 11] regress parameter values from performance targets under fixed topologies. Graph-based models [16] incorporate topology-aware representations to predict performance metrics from netlists. However, these approaches focus on forward prediction or black-box sizing and do not support inverse design across varied topologies. In contrast, FALCON unifies forward modeling and parameter inference in a single differentiable architecture that generalizes to unseen netlists.

Layout-aware sizing and parasitic modeling have been explored to mitigate schematic-to-layout mismatch. Parasitic-aware methods [25] integrate pre-trained parasitic estimators into Bayesian optimization loops for fixed schematics. While effective for estimation, these approaches rely on time-consuming black-box search and lack inverse design capabilities. Other methods, such as ALIGN [26] and LayoutCopilot [27], generate layouts from fully sized netlists using ML-based constraint extraction or scripted interactions, but assume fixed parameters and do not support cooptimization or differentiable inverse design. In contrast, FALCON embeds layout objectives

<sup>&</sup>lt;sup>1</sup>Code, trained models, and dataset will be released upon publication.

directly into the learning loss, enabling joint optimization of sizing and layout without relying on external parasitic models. For mm-wave circuits, our layout-aware loss captures frequency-sensitive constraints via simplified models that implicitly reflect DRC rules, EM coupling, and performancecritical factors such as quality factor and self-resonance frequency.

Datasets for analog design are often limited to symbolic SPICE simulations or small-scale testbeds that do not reflect real-world design flows. AnalogGym [18] and AutoCkt [13] rely on synthetic circuits and symbolic simulators, lacking the process fidelity, noise characteristics, and layout-dependent behavior of foundry-calibrated flows. In contrast, FALCON is trained on a large-scale dataset constructed from over one million Cadence-simulated circuits across 20 topologies and five circuit categories, offering a substantially more realistic foundation for ML-driven analog design.

To the best of our knowledge, FALCON is the first framework to unify topology selection, parameter inference, and layout-aware optimization in a single end-to-end pipeline, validated at scale using industrial-grade Cadence simulations for mm-wave analog circuits. A qualitative comparison with representative prior work is provided in Appendix A.

## 91 3 A Large-Scale Dataset and Inverse Design Problem Formulation

#### 92 3.1 Dataset Overview

109

We construct a large-scale dataset of analog and RF circuits simulated using industry-grade Cadence

tools [28] with a 45nm CMOS process design kit (PDK). The dataset spans five widely used mm-wave

circuit types for wireless applications [29, 30]: low-noise amplifiers (LNAs) [31–34], mixers [35–38],

power amplifiers (PAs) [39–43], voltage amplifiers (VAs) [44–48], and voltage-controlled oscillators

(VCOs) [49–53]. Each circuit type is instantiated in four distinct topologies, resulting in a total of 20

expert-designed architectures.

For each topology, expert-designed schematics were implemented in Cadence Virtuoso, and key design parameters were manually identified based on their functional relevance. Parameter ranges 100 were specified by domain experts and systematically swept using Cadence ADE XL, enabling 101 parallelized Spectre simulations across the design space. For each configuration, performance 102 metrics—such as gain, bandwidth, and oscillation frequency—were extracted and recorded. Each 103 datapoint therefore includes the full parameter vector, the corresponding Cadence netlist, and the simulated performance metrics. The resulting dataset comprises over one million datapoints, capturing 105 a wide range of circuit behaviors and design trade-offs across diverse topologies. This large-scale, high-fidelity dataset forms the foundation for training and evaluating our inverse design pipeline. Detailed metric definitions and per-topology parameter ranges appear in Appendix B. 108

## 3.2 Graph-Based Circuit Representation

To enable flexible and topology-agnostic learning, we represent each analog circuit as a graph extracted from its corresponding Cadence netlist. Nodes correspond to voltage nets (i.e., electrical connection points), and edges represent circuit elements such as transistors, resistors, capacitors, or sources. Multi-terminal devices—such as transistors and baluns—are decomposed into multiple edges, and multiple components may connect the same node pair, resulting in heterogeneous, multi-edged graphs that preserve structural and functional diversity.

Recent works such as DICE [54] have explored transistor-level circuit-to-graph conversions for self-supervised learning, highlighting the challenges of faithfully capturing device structure and connectivity. In contrast, our approach maintains a native representation aligned with foundry-compatible netlists. Rather than flattening or reinterpreting device abstractions, we preserve symbolic parameters, multi-edge connections, and device-specific edge decomposition directly from the schematic source, enabling scalable learning across diverse analog circuit families.

To support learning over such structured graphs, each edge is annotated with a rich set of attributes:

(i) a **categorical device type**, specifying the component and connected terminal pair (e.g., NMOS drain—gate, resistor); (ii) **numeric attributes**, such as channel length or port resistance, fixed by the schematic; (iii) **parametric attributes**, defined symbolically in the netlist (e.g., W1, R3) and resolved numerically during preprocessing; (iv) **one-hot categorical features**, such as source type (DC, AC, or none); and (v) **computational attributes**, such as diffusion areas (Ad, As) derived from

sizing. This rule-based graph construction generalizes across circuit families without task-specific customization. Graphs in the FALCON dataset range from 4–40 nodes and 7–70 edges, reflecting the variability of practical analog designs. Further details on the graph representation and attribute encoding are provided in Appendix C.

#### 3.3 Inverse Design Problem Definition

132

154

155

159

173

In analog and RF circuit design, the traditional modeling process involves selecting a topology T and parameter vector x, then evaluating circuit behavior via simulation to obtain performance metrics y=f(T,x). This forward workflow depends heavily on designer intuition, manual tuning, and exhaustive parameter sweeps. Engineers typically simulate many candidate (T,x) pairs and select the one that best satisfies the target specification—a slow, costly, and unguided process.

In contrast, our goal is to perform *inverse design*: given a target performance specification  $y_{\text{target}}$ , we aim to directly infer a topology and parameter configuration (T,x) such that  $f(T,x) \approx y_{\text{target}}$ , without enumerating the full design space. This inverse problem is ill-posed and the search space is constrained by both device-level rules and layout-aware objectives.

Formally, the task is to find the optimal topology  $T^* \in \mathcal{T}$  and the optimal parameters  $x^* \in \mathbb{R}^p$  such that  $f(T^*, x^*) \approx y_{\text{target}}$  where  $f: \mathcal{T} \times \mathbb{R}^p \to \mathbb{R}^d$  the true performance function implemented by expensive Cadence simulations. In practice, f is nonlinear and non-invertible, making direct inversion intractable. FALCON addresses this challenge through a modular, three-stage pipeline:

Stage 1: Topology Selection. We frame topology selection as a classification problem over a curated set of K candidate topologies  $\{T_1, \ldots, T_K\}$ . Given a target specification  $y_{\text{target}}$ , a lightweight MLP selects the topology  $T^* \in \mathcal{T}$  most likely to satisfy it, reducing the need for exhaustive search.

Stage 2: Performance Prediction. Given a topology T and parameter vector x, we train a GNN  $f_{\theta}$  to predict the corresponding performance  $\hat{y} = f_{\theta}(T, x)$ . This model emulates the forward behavior of the simulator f, learning a continuous approximation of circuit performance across both seen and unseen topologies. By capturing the topology-conditioned mapping from parameters to performance,  $f_{\theta}$  serves as a differentiable surrogate that enables gradient-based inference in the next stage.

Stage 3: Layout-Aware Gradient Reasoning. Given  $y_{\text{target}}$  and a selected topology  $T^*$ , we infer a parameter vector  $x^*$  by minimizing a loss over the learned forward model  $f_{\theta}$ . Specifically, we solve:

$$x^* = \arg\min_{x} \ \mathcal{L}_{perf}(f_{\theta}(T^*, x), y_{target}) + \lambda \mathcal{L}_{layout}(x), \tag{1}$$

where  $\mathcal{L}_{perf}$  measures prediction error, and  $\mathcal{L}_{layout}$  encodes differentiable layout-related constraints such as estimated area and soft design-rule penalties. Optimization is performed via gradient descent, allowing layout constraints to guide the search through a physically realistic parameter space.

## 4 Stage 1: Performance-Driven Topology Selection

Task Setup. We formulate topology selection as a supervised classification task over a fixed library of 20 expert-designed circuit topologies  $\mathcal{T}=\{T_1,T_2,\ldots,T_{20}\}$ . Rather than generating netlists from scratch—which often leads to invalid or impractical circuits—we select from a vetted set of designer-verified topologies. This ensures that all candidates are functionally correct, layout-feasible, and manufacturable. While expanding the topology set requires retraining, our lightweight MLP classifier enables rapid updates, making the approach scalable. This formulation also aligns with practical design workflows, where quickly identifying a viable initial topology is critical.

Each datapoint is represented by a 16-dimensional performance vector of key analog/RF metrics. We normalize features using z-scores computed from the training set. Missing metrics (e.g., oscillation frequency for amplifiers) are imputed with zeros, yielding zero-centered, fixed-length vectors that retain task-relevant variation. Dataset splits are stratified to preserve class balance across training, validation, and test sets. We assume each target vector is realizable by at least one topology in  $\mathcal{T}$ , though the library can be extended with new designs.

**Model Architecture and Training.** We train a 5-layer MLP with hidden size 256 and ReLU activations for this problem. The model takes the normalized performance vector  $y_{\text{target}} \in \mathbb{R}^{16}$  as

<sup>&</sup>lt;sup>2</sup>See Appendix B for the complete definitions of performance metrics.

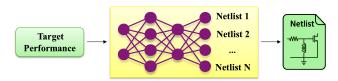

Figure 2: In Stage 1, an MLP classifier selects the most suitable circuit topology from a library of human-designed netlists, conditioned on the target performance specification.

Table 1: Classification performance on topology selection.

| Metric            | Score (%) |

|-------------------|-----------|

| Accuracy          | 99.57     |

| Balanced Accuracy | 99.33     |

| Macro Precision   | 99.27     |

| Macro Recall      | 99.33     |

| Macro F1          | 99.30     |

| Micro F1          | 99.57     |

input and outputs a probability distribution over 20 candidate topologies. The predicted topology is selected as  $T^* = \arg\max_{T_k \in \mathcal{T}} \mathrm{MLP}(y_{\mathrm{target}})_k$ . We train the model using a cross-entropy loss and the Adam optimizer [55], with a batch size of 256. An overview of this process is shown in Figure 2.

**Evaluation.** We assess classification performance using accuracy, balanced accuracy, macro precision, macro recall, macro F1, and micro F1 scores on the test set. As summarized in Table 1, the classifier achieves an overall accuracy of 99.57%, with macro F1 of 99.30% and balanced accuracy of 99.33%, demonstrating strong generalization across all 20 circuit topologies. Micro F1 (identical to accuracy in the multiclass setting) reaches 99.57%, while macro metrics—averaged equally across classes—highlight robustness to class imbalance. Additional visualizations and detailed analysis are presented in Appendix D. Seed-averaged results with 95% confidence intervals are provided in Appendix E.

## 5 Stage 2: Generalizable Forward Modeling for Performance Prediction

**Task Setup.** The goal of Stage 2 is to learn a differentiable approximation of the circuit simulator that maps a topology T and parameter vector x to a performance prediction  $\hat{y} = f_{\theta}(T, x)$ , where  $\hat{y} \in \mathbb{R}^{16}$ . Unlike black-box simulators, this learned forward model enables efficient performance estimation and supports gradient-based parameter inference in Stage 3. The model is trained to generalize across circuit families and can be reused on unseen topologies with minimal fine-tuning.

Each datapoint consists of a graph-structured Cadence netlist annotated with resolved parameter values and the corresponding performance metrics. We frame the learning task as a supervised regression problem. Since not all performance metrics apply to every topology (e.g., oscillation frequency is undefined for amplifiers), we train the model using a **masked mean squared error** loss:

$$\mathcal{L}_{\text{masked}} = \frac{1}{\sum_{i} m_{i}} \sum_{i=1}^{d} m_{i} \cdot (\hat{y}_{i} - y_{i})^{2}, \tag{2}$$

where  $m_i = 1$  if the *i*-th metric is defined for the current sample, and 0 otherwise.

Model Architecture and Training. Each circuit is represented as an undirected multiedge graph with voltage nets as nodes and circuit components as edges. All circuit parameters—both fixed and sweepable—are assigned to edges, along with categorical device types and one-hot encoded indicators. For each edge (u,v), these attributes are concatenated to form a unified feature vector  $x_{uv}$ . The feature set is consistent within each component type but varies across types (e.g., NMOS vs. inductor), reflecting the structure defined in Section 3.2.

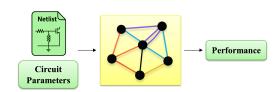

Figure 3: In Stage 2, a custom edge-centric GNN maps an undirected multi-edge graph constructed from the circuit netlist to a performance vector.

To account for component heterogeneity, we apply **type-specific MLP encoders**  $\phi_{\rm enc}^{(t)}$  to each edge feature vector, producing initial embeddings  $e_{uv}^{(0)} = \phi_{\rm enc}^{(t)}(x_{uv})$ , where t is the component type. These embeddings are updated via a 4-layer **edge-centric message-passing GNN** with shared weights. At

each layer  $\ell$ , for each node u, we first compute the node hidden state using the edge embeddings of all neighbors of the node u,  $\mathcal{N}(u)$ . Then, for each edge (u,v) in the circuit graph, we compute the edge embedding at the next layer  $\ell+1$  is using the edge embedding  $e_{uv}^{(\ell)}$  and the hidden node states forming the edge (u,v) at the current layer  $\ell$  as follows:

$$h_u^{(\ell)} = \sum_{w \in \mathcal{N}(u)} \phi_{\text{MSG}}(e_{wu}^{(\ell)}), \quad e_{uv}^{(\ell+1)} = \phi_{\text{UPD}}(e_{uv}^{(\ell)}, h_u^{(\ell)}, h_v^{(\ell)}),$$

where  $\phi_{\text{MSG}}$ ,  $\phi_{\text{UPD}}$  are the message and update parameters of message-passing GNN and  $h_u^{(\ell)}$ ,  $h_v^{(\ell)}$  are the hidden states for the nodes forming the edge (u,v) respectively. After message passing [56], final edge embeddings  $e_{uv}^{(L)}$  are aggregated to form a graph-level representation  $z_{\text{graph}} = \sum_{(u,v)} e_{uv}^{(L)}$ , which is decoded by a fully connected MLP (hidden size 256) to predict the 16-dimensional performance vector  $\hat{y} \in \mathbb{R}^{16}$ . An overview of this GNN-based forward prediction pipeline is shown in Figure 3.

To stabilize training, physical parameters are rescaled by their expected units (e.g. resistance by  $10^3$ ), and performance targets are normalized to z-scores using training statistics. We train the model using the Adam optimizer (learning rate  $10^{-3}$ , batch size 256) and a ReduceLROnPlateau scheduler. Xavier uniform initialization is used for all layers, and early stopping is based on validation loss. We adopt the same splits as in Section 4 for consistency in evaluation.

**Evaluation.** We evaluate the accuracy of the GNN forward model  $f_{\theta}$  on a test set drawn from 19 of the 20 topologies. One topology—RVCO—is entirely excluded from training, validation, and test splits to assess generalization to unseen architectures. Additional generalization results are included in Appendix F. Prediction quality is measured using standard regression metrics: coefficient of determination  $(R^2)$ , root mean squared error (RMSE), and mean absolute error (MAE), computed independently for each of the 16 performance metrics. We also report the *mean relative error per metric*, computed as the average across all test samples where each metric is defined. As summarized in Table 2, the model achieves high accuracy across all dimensions, with an average  $R^2$  of 0.972.

200

201

202

203

204

205

206 207

208

209

210

211

212

214

215

216

217

218

219

220 221

222

223

225

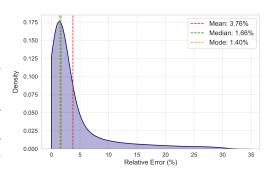

Figure 4: Distribution of relative error (%) across the test set for the GNN forward model. Plot is trimmed at the 95th percentile.

To evaluate end-to-end prediction accuracy at the sample level, we compute the *mean relative error* per instance, defined as the average relative error across all valid (non-masked) performance metrics for each test sample. Figure 4 shows the distribution of this quantity across the test set (trimmed at the 95th percentile to reduce the impact of outliers). The distribution is sharply concentrated, indicating that most predictions closely match their corresponding target vectors. Without percentile trimming, the overall mean relative error across the full test set is 9.09%. Seed-averaged results with 95% confidence intervals are provided in Appendix E.

Table 2: Prediction accuracy of the forward GNN on all 16 circuit performance metrics.

| Metric         | DCP   | VGain | PGain | CGain | $\mathbf{S}_{11}$ | $S_{22}$ | NF    | BW    | OscF  | TR    | OutP  | $\mathbf{P}_{\mathbf{SAT}}$ | DE    | PAE   | PN     | VSwg  |

|----------------|-------|-------|-------|-------|-------------------|----------|-------|-------|-------|-------|-------|-----------------------------|-------|-------|--------|-------|

| Unit           | mW    | dB    | dB    | dB    | dB                | dB       | dB    | GHz   | GHz   | GHz   | dBm   | dBm                         | %     | %     | dBc/Hz | mV    |

| R <sup>2</sup> | 1.0   | 1.0   | 0.99  | 1.0   | 0.93              | 1.0      | 0.99  | 0.98  | 0.97  | 0.83  | 0.97  | 1.0                         | 1.0   | 1.0   | 0.89   | 1.0   |

| RMSE           | 0.27  | 0.101 | 0.536 | 0.833 | 1.515             | 0.21     | 0.534 | 0.972 | 0.723 | 0.293 | 0.91  | 0.095                       | 0.226 | 0.143 | 2.536  | 0.071 |

| MAE            | 0.198 | 0.072 | 0.208 | 0.188 | 0.554             | 0.12     | 0.2   | 0.376 | 0.184 | 0.097 | 0.238 | 0.066                       | 0.163 | 0.105 | 1.159  | 0.046 |

| Rel. Err.      | 11.2% | 2.6%  | 19.0% | 6.1%  | 11.4%             | 1.9%     | 4.5%  | 6.5%  | 0.6%  | 6.5%  | 4.6%  | 4.4%                        | 4.6%  | 11.0% | 1.3%   | 1.4%  |

## 6 Stage 3: Layout-Aware Parameter Inference via Gradient Reasoning

**Task Setup.** Given a target performance vector  $y_{\text{target}}$  and a selected topology  $T^*$ , the goal of Stage 3 is to recover a parameter vector  $x^*$  that minimizes a total loss combining performance error and layout-aware penalties, using the learned forward model  $f_{\theta}$  from Stage 2. This formulation enables instance-wise inverse design without requiring circuit-level simulation.

Figure 5: In Stage 3, gradient reasoning iteratively updates parameters to minimize a loss combining performance error and layout cost, computed via a differentiable analytical model.

To initialize optimization, we perturb domain-specific scale factors (e.g.,  $10^{-12}$  for capacitors) to sample a plausible starting point  $x_0$ . Parameters are iteratively updated via gradient descent, guided by both functional and physical objectives. Topology-specific constants are held fixed, and parameter values are clipped to remain within valid domain bounds throughout the process.

Loss Function. The total loss follows the structure defined in Eqn 1, jointly minimizing performance mismatch and layout cost:

$$\mathcal{L}_{\text{total}} = \mathcal{L}_{\text{perf}} + \lambda_{\text{area}} \cdot \mathcal{L}_{\text{layout}} \cdot g(\mathcal{L}_{\text{perf}}), \tag{3}$$

where  $\mathcal{L}_{perf}$  is the masked mean squared error (see Eqn 2) between predicted and target performance vectors, and  $\mathcal{L}_{layout}$  is a normalized area penalty derived from analytical layout equations. To prioritize functionality, layout loss is softly gated by:

$$g(\mathcal{L}_{perf}) = 1 - \sigma \left( \gamma (\mathcal{L}_{perf} - \tau) \right),$$

which attenuates layout penalties when performance error exceeds a threshold  $\tau$ , encouraging the model to first achieve functionality before optimizing for layout compactness.

We set  $\tau=0.05$ ,  $\gamma=50$ , and normalize layout area by 1 mm² to stabilize gradients. The layout weight  $\lambda_{\rm area}=0.02$  is chosen empirically to balance performance accuracy and physical realism without dominating the loss. This gated formulation supports manufacturable parameter recovery and reflects the broader paradigm of physics-informed learning [57]. Further discussion on user-defined objectives is provided in Appendix G.

243

245

246

247

248

249

250

251 252

253

254

255

261

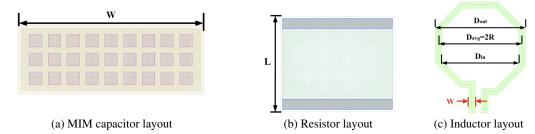

Differentiable Layout Modeling. In mm-wave analog design, layout is not a downstream concern but a critical determinant of circuit performance—particularly for passive components. Substrate coupling, proximity effects, and DRC-imposed geometries directly affect key metrics such as resonance frequency, quality factor, and impedance matching. To incorporate these effects, we introduce a differentiable layout model that computes total physical area analytically from circuit parameters. This enables layout constraints to directly guide parameter optimization during inverse design. By minimizing the layout area in distributed mm-wave circuits [58], unwanted signal loss [59] is reduced, the self-resonance frequency of passives can increase [60], and phase and amplitude mismatches across signal paths [61] can be reduced.

The layout model is deterministic and non-learned. It estimates area contributions from passive components—capacitors, inductors, and resistors—as these dominate total area and exhibit layout-sensitive behavior. Active devices (e.g., MOSFETs) are excluded since their geometries are fixed by the PDK and are negligible [62]. For a given parameter vector x, the total layout loss is computed as:

$$\mathcal{L}_{\text{layout}}(x) = \sum_{e \in \mathcal{E}_{\text{passive}}} A_e(x),$$

where  $\mathcal{E}_{\text{passive}}$  is the set of passive elements, and  $A_e(x)$  is the area of the created layout for the passive component based on analytical physics-based equations. The area of element e is estimated based on its 2D dimensions (e.g.,  $A = W \cdot L$  for resistors and capacitors). This area is normalized and used as a differentiable penalty in the optimization objective (see Eqn 3). Further implementation details are provided in Appendix H.

**Gradient Reasoning Procedure.** Starting from the initialized parameter vector x, we iteratively update parameters via gradient reasoning. At each step, the frozen forward model  $f_{\theta}$  predicts the

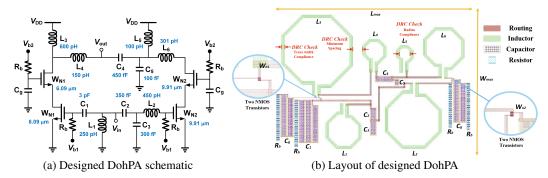

Figure 6: Stage 3 results for a synthesized DohPA. The schematic (a) reflects optimized parameters to meet the target specification. The layout (b) is DRC-compliant and physically realizable. The final design achieves a mean relative error of 5.4% compared to the target performance.

performance  $\hat{y} = f_{\theta}(T, x)$ , and the total loss  $\mathcal{L}_{\text{total}}$  is evaluated. Gradients are backpropagated with respect to x, and updates are applied using the Adam optimizer. Optimization proceeds for a fixed number of steps, with early stopping triggered if the loss fails to improve over a predefined window.

To handle varying circuit difficulty and initialization quality, we employ an adaptive learning rate strategy. Each instance begins with a moderate learning rate  $(10^{-6})$ , refined during optimization via a ReduceLROnPlateau scheduler. If the solution fails to meet thresholds on performance error or layout area, optimization restarts with a more exploratory learning rate. This adjustment balances exploration and fine-tuning, enabling rapid convergence to physically valid solutions, typically within milliseconds to under one second per instance. An overview is shown in Figure 5.

**Evaluation.** We evaluate Stage 3 on 9,500 test instances (500 per topology) using our gradient-based optimization pipeline. A design is considered *converged* if it meets both: (i) a predicted mean relative error below 10%, and (ii) a layout area under a topology-specific bound—1 mm<sup>2</sup> for most circuits and 1.5 mm<sup>2</sup> for DLNA, DohPA, and ClassBPA. The 10% error threshold reflects the forward model's  $\sim 9\%$  average prediction error (Section 5). A design is deemed *successful* if its final Cadence-simulated performance deviates from the target by less than 20%, confirming real-world viability. Our method achieves a success rate of **78.5**% and a mean relative error of **17.7**% across converged designs, with average inference time under 1 second on a MacBook CPU. Notably, success rate is coupled with convergence threshold: tighter error bounds yield higher accuracy with more iterations.

To illustrate the effectiveness of our pipeline, Figure 6 shows a representative result for the DohPA topology: the synthesized schematic is shown on the left, and the corresponding layout is on the right. These results confirm that the recovered parameters are both functionally accurate and physically realizable. Together, they demonstrate that FALCON enables layout-aware inverse design within a single differentiable pipeline—a capability not supported by existing analog design frameworks.

#### 7 Conclusion and Future Work

We presented FALCON, a modular framework for end-to-end analog and RF circuit design that unifies topology selection, performance prediction, and layout-aware parameter optimization. Trained on over one million Cadence-simulated mm-wave circuits, FALCON combines a lightweight MLP, a generalizable GNN, and differentiable gradient reasoning to synthesize circuits from specification to layout-constrained parameters. FALCON achieves >99% topology selection accuracy, <10% prediction error, and efficient inverse design—all within sub-second inference. In addition, the GNN forward model generalizes to unseen topologies with minimal fine-tuning, supporting broad practical deployment. Further discussion of efficiency and limitations are provided in Appendix I.

In future work, we aim to expand the topology library and support hierarchical macroblocks for scalable design beyond the cell level. We also plan to extend the dataset to cover multiple operating frequencies, enabling validation across diverse bands, and to enhance the layout-aware optimization with learned parasitic models, EM-informed constraints, and electromigration considerations for more accurate post-layout estimation. Finally, integrating models for generative topology synthesis represents a promising step toward general-purpose analog design automation.

#### References

301

- 302 [1] Vilem Kledrowetz, Roman Prokop, Lukas Fujcik, and Jiri Haze. A fully differential analog front-end for 303 signal processing from emg sensor in 28 nm fdsoi technology. Sensors, 23(7), 2023.

- Wei Hong, Zhi Hao Jiang, Chao Yu, Debin Hou, Haiming Wang, Chong Guo, Yun Hu, Le Kuai, Yingrui

Yu, Zhengbo Jiang, Zhe Chen, Jixin Chen, Zhiqiang Yu, Jianfeng Zhai, Nianzu Zhang, Ling Tian, Fan Wu,

Guangqi Yang, Zhang-Cheng Hao, and Jian Yi Zhou. The role of millimeter-wave technologies in 5g/6g

wireless communications. *IEEE Journal of Microwaves*, 1(1):101–122, 2021.

- 308 [3] Yingying Chi, Haifeng Zhang, Zhe Zheng, Rui Liu, Lei Qiao, and Wenpeng Cui. Analog front-end 309 circuit design for wireless sensor system-on-chip. In 2020 IEEE 4th Information Technology, Networking, 310 Electronic and Automation Control Conference (ITNEC), volume 1, pages 38–42, 2020.

- [4] Xuyang Liu, Md. Hedayatullah Maktoomi, Mahdi Alesheikh, Payam Heydari, and Hamidreza Aghasi. A

cmos 49–63-ghz phase-locked stepped-chirp fmcw radar transceiver. *IEEE Journal of Solid-State Circuits*,

pages 1–15, 2025.

- [5] Med Nariman, Farid Shirinfar, Anna Papió Toda, Sudhakar Pamarti, Ahmadreza Rofougaran, and Franco

De Flaviis. A compact 60-ghz wireless power transfer system. *IEEE Transactions on Microwave Theory* and Techniques, 64(8):2664–2677, 2016.

- [6] Phillip E Allen and Douglas R Holberg. CMOS analog circuit design. Elsevier, 2011.

- 318 [7] Willy M. C. Sansen. analog design essentials. SpringerLink, 2011.

- [8] Shady A Abdelaal, Ahmed Hussein, and Hassan Mostafa. A bayesian optimization framework for analog circuits optimization. In 2020 15th International Conference on Computer Engineering and Systems

(ICCES), pages 1–4. IEEE, 2020.

- [9] Zehao Dong, Weidong Cao, Muhan Zhang, Dacheng Tao, Yixin Chen, and Xuan Zhang. CktGNN: Circuit

graph neural network for electronic design automation. In *The Eleventh International Conference on Learning Representations*, 2023.

- 10 Hanrui Wang, Kuan Wang, Jiacheng Yang, Linxiao Shen, Nan Sun, Hae-Seung Lee, and Song Han. Gcn-rl circuit designer: Transferable transistor sizing with graph neural networks and reinforcement learning. In 2020 57th ACM/IEEE Design Automation Conference (DAC), pages 1–6, 2020.

- [11] Dmitrii Krylov, Pooya Khajeh, Junhan Ouyang, Thomas Reeves, Tongkai Liu, Hiba Ajmal, Hamidreza

Aghasi, and Roy Fox. Learning to design analog circuits to meet threshold specifications. In *Proceedings* of the 40th International Conference on Machine Learning, ICML'23. JMLR.org, 2023.

- 131 [12] Hanrui Wang, Jiacheng Yang, Hae-Seung Lee, and Song Han. Learning to design circuits. *arXiv preprint* arXiv:1812.02734, 2018.

- [13] Keertana Settaluri, Ameer Haj-Ali, Qijing Huang, Kourosh Hakhamaneshi, and Borivoje Nikolic. Autockt:

deep reinforcement learning of analog circuit designs. In *Proceedings of the 23rd Conference on Design*,

Automation and Test in Europe, DATE '20, page 490–495, San Jose, CA, USA, 2020. EDA Consortium.

- Yaguang Li, Yishuang Lin, Meghna Madhusudan, Arvind Sharma, Sachin Sapatnekar, Ramesh Harjani,

and Jiang Hu. A circuit attention network-based actor-critic learning approach to robust analog transistor

sizing. In 2021 ACM/IEEE 3rd Workshop on Machine Learning for CAD (MLCAD), pages 1–6, 2021.

- [15] Wenlong Lyu, Pan Xue, Fan Yang, Changhao Yan, Zhiliang Hong, Xuan Zeng, and Dian Zhou. An efficient bayesian optimization approach for automated optimization of analog circuits. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 65(6):1954–1967, 2017.

- [16] Kourosh Hakhamaneshi, Marcel Nassar, Mariano Phielipp, Pieter Abbeel, and Vladimir Stojanovic.

Pretraining graph neural networks for few-shot analog circuit modeling and design. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 42(7):2163–2173, 2022.

- [17] Morteza Fayazi, Morteza Tavakoli Taba, Ehsan Afshari, and Ronald Dreslinski. Angel: Fully-automated

analog circuit generator using a neural network assisted semi-supervised learning approach. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 2023.

- Jintao Li, Haochang Zhi, Ruiyu Lyu, Wangzhen Li, Zhaori Bi, Keren Zhu, Yanhan Zeng, Weiwei Shan,

Changhao Yan, Fan Yang, Yun Li, and Xuan Zeng. Analoggym: An open and practical testing suite for

analog circuit synthesis. In *International Conference on Computer Aided Design*, 2024.

- [19] Chen-Chia Chang, Yikang Shen, Shaoze Fan, Jing Li, Shun Zhang, Ningyuan Cao, Yiran Chen, and Xin

Zhang. Lamagic: Language-model-based topology generation for analog integrated circuits. arXiv preprint

arXiv:2407.18269, 2024.

- Yao Lai, Sungyoung Lee, Guojin Chen, Souradip Poddar, Mengkang Hu, David Z Pan, and Ping Luo.

Analogcoder: Analog circuit design via training-free code generation. In *Proceedings of the AAAI Conference on Artificial Intelligence*, volume 39, pages 379–387, 2025.

- Weidong Cao, Mouhacine Benosman, Xuan Zhang, and Rui Ma. Domain knowledge-based automated

analog circuit design with deep reinforcement learning. arXiv preprint arXiv:2202.13185, 2022.

- Ahmet Faruk Budak, Miguel Gandara, Wei Shi, David Z. Pan, Nan Sun, and Bo Liu. An efficient analog circuit sizing method based on machine learning assisted global optimization. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 41(5):1209–1221, 2022.

- [23] Asal Mehradfar, Xuzhe Zhao, Yue Niu, Sara Babakniya, Mahdi Alesheikh, Hamidreza Aghasi, and Salman

Avestimehr. AICircuit: A Multi-Level Dataset and Benchmark for AI-Driven Analog Integrated Circuit

Design. Machine Learning and the Physical Sciences Workshop @ NeurIPS, 2024.

- Asal Mehradfar, Xuzhe Zhao, Yue Niu, Sara Babakniya, Mahdi Alesheikh, Hamidreza Aghasi, and Salman

Avestimehr. Supervised learning for analog and rf circuit design: Benchmarks and comparative insights.

arXiv preprint arXiv:2501.11839, 2025.

- [25] Mingjie Liu, Walker J. Turner, George F. Kokai, Brucek Khailany, David Z. Pan, and Haoxing Ren.

Parasitic-aware analog circuit sizing with graph neural networks and bayesian optimization. In 2021

Design, Automation & Test in Europe Conference & Exhibition (DATE), pages 1372–1377, 2021.

- [26] Tonmoy Dhar, Kishor Kunal, Yaguang Li, Meghna Madhusudan, Jitesh Poojary, Arvind K Sharma, Wenbin

Xu, Steven M Burns, Ramesh Harjani, Jiang Hu, et al. Align: A system for automating analog layout.

IEEE Design & Test, 38(2):8–18, 2020.

- Bingyang Liu, Haoyi Zhang, Xiaohan Gao, Zichen Kong, Xiyuan Tang, Yibo Lin, Runsheng Wang, and

Ru Huang. Layoutcopilot: An Ilm-powered multi-agent collaborative framework for interactive analog

layout design. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2025.

- [28] Antonio J Lopez Martin. Cadence design environment. New Mexico State University, Tutorial paper, 35,

2002.

- 379 [29] Sorin Voinigescu. High-frequency integrated circuits. Cambridge University Press, 2013.

- 380 [30] Behzad Razavi. RF microelectronics, volume 2. Prentice hall New York, 2012.

- [31] Thomas H. Lee. The Design of CMOS Radio-Frequency Integrated Circuits. Cambridge University Press,

2nd edition, 2004.

- [32] John R. Long and Michael A. Copeland. The design of low-noise cmos rf amplifiers. *IEEE Journal of Solid-State Circuits*, 32(2):292–302, 1997.

- 385 [33] Ali M. Niknejad. mm-Wave Silicon Technology: 60 GHz and Beyond. Springer, 2008.

- Xiaohua Fan, Heng Zhang, and Edgar SÁnchez-Sinencio. A noise reduction and linearity improvement

technique for a differential cascode lna. *IEEE Journal of Solid-State Circuits*, 43(3):588–599, 2008.

- 388 [35] B. Henderson and E. Camargo. *Microwave Mixer Technology and Applications*. Microwave & RF. Artech House, 2013.

- 390 [36] B. Gilbert. A precise four-quadrant multiplier with subnanosecond response. *IEEE Journal of Solid-State Circuits*, 3(4):365–373, 1968.

- [37] Krenar Komoni, Sameer Sonkusale, and Geoff Dawe. Fundamental performance limits and scaling of

a cmos passive double-balanced mixer. In 2008 Joint 6th International IEEE Northeast Workshop on

Circuits and Systems and TAISA Conference, pages 297–300, 2008.

- [38] S. Chehrazi, R. Bagheri, and A.A. Abidi. Noise in passive fet mixers: a simple physical model. In

Proceedings of the IEEE 2004 Custom Integrated Circuits Conference (IEEE Cat. No.04CH37571), pages

375–378, 2004.

- 398 [39] Hua Wang, Peter M. Asbeck, and Christian Fager. Millimeter-wave power amplifier integrated circuits for high dynamic range signals. *IEEE Journal of Microwaves*, 1(1):299–316, 2021.

- 400 [40] M.K. Kazimierczuk. RF Power Amplifiers. Wiley, 2014.

- [41] F.H. Raab, P. Asbeck, S. Cripps, P.B. Kenington, Z.B. Popovic, N. Pothecary, J.F. Sevic, and N.O. Sokal.

Power amplifiers and transmitters for rf and microwave. *IEEE Transactions on Microwave Theory and Techniques*, 50(3):814–826, 2002.

- 404 [42] Narek Rostomyan, Mustafa Özen, and Peter Asbeck. 28 ghz doherty power amplifier in cmos soi with 28 405 *IEEE Microwave and Wireless Components Letters*, 28(5):446–448, 2018.

- 406 [43] Morteza Abbasi, Torgil Kjellberg, Anton de Graauw, Edwin van der Heijden, Raf Roovers, and Herbert

407 Zirath. A broadband differential cascode power amplifier in 45 nm cmos for high-speed 60 ghz system-on 408 chip. In 2010 IEEE Radio Frequency Integrated Circuits Symposium, pages 533–536, 2010.

- 409 [44] Behzad Razavi. Design of Analog CMOS Integrated Circuits. McGraw-Hill Education, 2016.

- [45] S. Karthikeyan, S. Mortezapour, A. Tammineedi, and E.K.F. Lee. Low-voltage analog circuit design based

on biased inverting opamp configuration. *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, 47(3):176–184, 2000.

- 413 [46] Tae Wook Kim. A common-gate amplifier with transconductance nonlinearity cancellation and its high-414 frequency analysis using the volterra series. *IEEE Transactions on Microwave Theory and Techniques*, 57 415 (6):1461–1469, 2009.

- 416 [47] T. Lehmann and M. Cassia. 1-v power supply cmos cascode amplifier. *IEEE Journal of Solid-State Circuits*, 36(7):1082–1086, 2001.

- 418 [48] H.-J. Song and C.-K. Kim. An mos four-quadrant analog multiplier using simple two-input squaring circuits with source followers. *IEEE Journal of Solid-State Circuits*, 25(3):841–848, 1990.

- 420 [49] N. R. Sivaraaj and K. K. Abdul Majeed. A comparative study of ring vco and lc-vco: Design, performance analysis, and future trends. *IEEE Access*, 11:127987–128017, 2023.

- 422 [50] Cao Wan, Taotao Xu, Xiang Yi, and Quan Xue. A current-reused vco with inductive-transformer feedback 423 technique. *IEEE Transactions on Microwave Theory and Techniques*, 70(5):2680–2689, 2022.

- Tuan Thanh Ta, Suguru Kameda, Tadashi Takagi, and Kazuo Tsubouchi. A 5ghz band low noise and wide

tuning range si-cmos vco. In 2009 IEEE Radio Frequency Integrated Circuits Symposium, pages 571–574,

2009.

- 427 [52] R. Aparicio and A. Hajimiri. A noise-shifting differential colpitts vco. *IEEE Journal of Solid-State Circuits*, 37(12):1728–1736, 2002.

- 429 [53] Shruti Suman, K. G. Sharma, and P. K. Ghosh. Analysis and design of current starved ring vco. In

430 2016 International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT), pages

431 3222–3227, 2016.

- 432 [54] Sungyoung Lee, Ziyi Wang, Seunggeun Kim, Taekyun Lee, and David Z Pan. Self-supervised graph 433 contrastive pretraining for device-level integrated circuits. *arXiv preprint arXiv:2502.08949*, 2025.

- 434 [55] Diederik P Kingma and Jimmy Ba. Adam: A method for stochastic optimization. *arXiv preprint* 435 *arXiv:1412.6980*, 2014.

- [56] Justin Gilmer, Samuel S Schoenholz, Patrick F Riley, Oriol Vinyals, and George E Dahl. Neural message

passing for quantum chemistry. In *International conference on machine learning*, pages 1263–1272.

PMLR, 2017.

- 439 [57] Maziar Raissi, Paris Perdikaris, and George Em Karniadakis. Physics informed deep learning (part i):

440 Data-driven solutions of nonlinear partial differential equations. *arXiv preprint arXiv:1711.10561*, 2017.

- 441 [58] A. Dounavis, R. Achar, and M.S. Nakhla. Efficient passive circuit models for distributed networks with 442 frequency-dependent parameters. *IEEE Transactions on Advanced Packaging*, 23(3):382–392, 2000.

- 443 [59] Shen Wang, M.A. de Rooij, W.G. Odendaal, J.D. van Wyk, and D. Boroyevich. Reduction of high 444 frequency conduction losses using a planar litz structure. *IEEE Transactions on Power Electronics*, 20(2):

445 261–267, 2005.

- 446 [60] Tejinder Singh and Raafat R Mansour. Miniaturized 6-bit phase-change capacitor bank with improved

447 self-resonance frequency and q. In 2022 52nd European Microwave Conference (EuMC), pages 572–575.

448 IEEE, 2022.

- (449 [61] Chenxi Zhao, Xing Zeng, Lin Zhang, Huihua Liu, Yiming Yu, Yunqiu Wu, and Kai Kang. A 37–40-ghz low-phase-imbalance cmos attenuator with tail-capacitor compensation technique. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 67(10):3400–3409, 2020.

- 452 [62] Michele Spasaro and Domenico Zito. Millimeter-wave integrated silicon devices: Active versus pas-453 sive—the eternal struggle between good and evil. In 2019 International Semiconductor Conference (CAS), 454 pages 11–20. IEEE, 2019.

- [63] Laurens Van der Maaten and Geoffrey Hinton. Visualizing data using t-sne. *Journal of machine learning research*, 9(11), 2008.

## 457 A Qualitative Comparison with Prior Work

To contextualize FALCON within the broader landscape of analog circuit design automation, we provide a qualitative comparison against representative prior works in Table 3. This comparison spans key capabilities including topology selection, parameter inference, performance prediction, layout awareness, and simulator fidelity. We additionally assess reproducibility via dataset and code availability, and introduce a new axis—**RF/mm-wave** support—to highlight methods evaluated on high-frequency circuit blocks such as LNAs, mixers, and VCOs. Compared to existing approaches, FALCON is the only framework that unifies all these dimensions while maintaining foundry-grade fidelity and open-source accessibility. Definitions for each comparison axis are provided in Table 4.

Table 3: Qualitative comparison of FALCON with prior works across key capabilities in analog circuit design automation.

| Method             | Topology<br>Selection | Parameter<br>Inference | Performance<br>Prediction | Layout<br>Awareness | Foundry<br>Grade            | RF/<br>mm-Wave | Public<br>Dataset | Public<br>Code        |  |

|--------------------|-----------------------|------------------------|---------------------------|---------------------|-----------------------------|----------------|-------------------|-----------------------|--|

| CktGNN [9]         | ~                     | V                      | ×                         | ×                   | ✗ (SPICE)                   | ×              | ~                 | ~                     |  |

| LaMAGIC [19]       | ~                     | ×                      | ×                         | ×                   | <b>✗</b> (SPICE)            | ×              | ×                 | ×                     |  |

| AnalogCoder [20]   | ~                     | ×                      | ×                         | ×                   | <b>✗</b> (SPICE)            | ×              | ~                 | ~                     |  |

| GCN-RL [10]        | ×                     | ~                      | ×                         | ×                   | ✓ (SPICE/Cadence)           | ×              | ×                 | <b>✗</b> (incomplete) |  |

| Cao et al. [21]    | ×                     | ~                      | ×                         | ×                   | ✓ (ADS/Cadence)             | ×              | ×                 | ×                     |  |

| BO-SPGP [15]       | ×                     | ~                      | ~                         | ×                   | ✓ (Cadence)                 | ×              | ×                 | ×                     |  |

| ESSAB [22]         | ×                     | ~                      | ~                         | ×                   | ✓ (Cadence)                 | ×              | ×                 | ×                     |  |

| AICircuit [23, 24] | ×                     | ~                      | ×                         | ×                   | ✓ (Cadence)                 | ~              | ~                 | <b>✓</b>              |  |

| Krylov et al. [11] | ×                     | ~                      | ×                         | ×                   | <b>✗</b> (SPICE)            | ×              | ~                 | ~                     |  |

| Deep-GEN [16]      | ×                     | ×                      | ~                         | ×                   | ✗ (SPICE)                   | ×              | ~                 | ~                     |  |

| Liu et al. [25]    | ×                     | ×                      | ×                         | ~                   | ✗ (SPICE + Parasitic Model) | ~              | ×                 | ×                     |  |

| ALIGN [26]         | ×                     | ×                      | ×                         | ~                   | ✓ (Cadence)                 | ~              | ~                 | ~                     |  |

| LayoutCopilot [27] | ×                     | ×                      | ×                         | ~                   | ✓ (Cadence)                 | ×              | ×                 | ×                     |  |

| AnalogGym [18]     | ×                     | ~                      | ×                         | ×                   | <b>✗</b> (SPICE)            | ×              | ~                 | ~                     |  |

| AutoCkt [13]       | ×                     | ~                      | ×                         | ×                   | ✓ (Cadence)                 | ×              | ×                 | ✗ (incomplete)        |  |

| L2DC [12]          | ×                     | ~                      | ×                         | ×                   | ✗ (SPICE)                   | ×              | ×                 | ×                     |  |

| CAN-RL [14]        | ×                     | ~                      | ×                         | ~                   | ✓ (Cadence)                 | ×              | ×                 | ×                     |  |

| AnGeL. [17]        | <b>~</b>              | ~                      | ~                         | ×                   | ✗ (SPICE)                   | ×              | ×                 | ×                     |  |

| FALCON (This work) | ~                     | ~                      | ~                         | ~                   | ✓ (Cadence)                 | ~              | ~                 | ~                     |  |

Table 4: Definitions of each comparison axis in Table 3.

| Column                 | Definition                                                                                                              |

|------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Topology Selection     | Does the method automatically select or predict circuit topology given a target specification?                          |

| Parameter Inference    | Does the method infer element-level parameters (e.g., transistor sizes, component values) as part of design generation? |

| Performance Prediction | Can the method predict circuit performance metrics (e.g., gain, bandwidth, noise) from topology and parameters?         |

| Layout Awareness       | Is layout considered during optimization or training (e.g., via area constraints, parasitics, or layout-informed loss)? |

| Dataset Fidelity       | Does the dataset reflect realistic circuit behavior (e.g., SPICE/Cadence simulations, PDK models)?                      |

| RF/mm-Wave             | Is the method evaluated on at least one RF or mm-wave circuit type that reflects high-frequency design challenges?      |

| Public Dataset         | Is the dataset used in the work publicly released for reproducibility and benchmarking?                                 |

| Public Code            | Is the implementation code publicly available and documented for reproducibility?                                       |

## **B** Dataset Details and Performance Metric Definitions

During dataset generation, each simulated circuit instance is annotated with a set of performance metrics that capture its functional characteristics. All simulations are performed at a fixed frequency of 30 GHz, ensuring consistency across circuit types and relevance to mm-wave design. A total of 16 metrics are defined across all circuits—spanning gain, efficiency, impedance matching, noise, and frequency-domain behavior—though the specific metrics used vary by topology. For example, phase noise is only applicable to oscillators. An overview of all performance metrics is provided in Table 5.

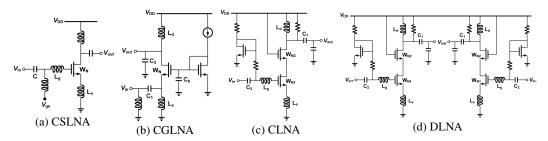

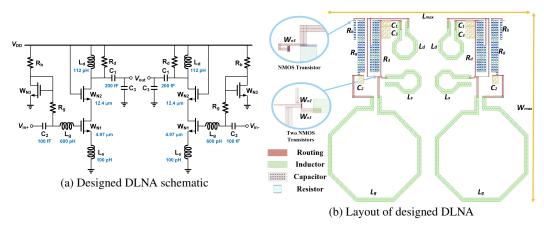

#### **B.1** Low-Noise Amplifiers (LNAs)

Low-noise amplifiers (LNAs) are critical components in receiver front-ends, responsible for amplifying weak antenna signals while introducing minimal additional noise. Their performance directly

influences downstream blocks such as mixers and analog-to-digital converters (ADCs), ultimately determining system-level fidelity [31]. To capture the architectural diversity of practical radio-frequency

(RF) designs, we include four widely used LNA topologies in this study—common-source LNA

(CSLNA), common-gate LNA (CGLNA), cascode LNA (CLNA), and differential LNA (DLNA)—as

shown in Figure 7.

Table 5: Overview of 16 performance metrics used during dataset generation.

| Performance Name             | Description                                                                               |

|------------------------------|-------------------------------------------------------------------------------------------|

| DC Power Consumption (DCP)   | Total power drawn from the DC supply indicating energy consumption of the circuit         |

| Voltage Gain (VGain)         | Ratio of output voltage amplitude to input voltage amplitude                              |

| Power Gain (PGain)           | Ratio of output power to input power                                                      |

| Conversion Gain (CGain)      | Ratio of output power at the desired frequency to input power at the original frequency   |

| $S_{11}$                     | Input reflection coefficient indicating impedance matching at the input terminal          |

| $S_{22}$                     | Output reflection coefficient indicating impedance matching at the output terminal        |

| Noise Figure (NF)            | Ratio of input signal-to-noise ratio to output signal-to-noise ratio                      |

| Bandwidth (BW)               | Frequency span over which the circuit maintains specified performance characteristics     |

| Oscillation Frequency (OscF) | Steady-state frequency at which the oscillator generates a periodic signal                |

| Tuning Range (TR)            | Range of achievable oscillation frequencies through variation of control voltages         |

| Output Power (OutP)          | Power delivered to the load                                                               |

| P <sub>SAT</sub>             | Maximum output power level beyond which gain compression begins to occur                  |

| Drain Efficiency (DE)        | Ratio of RF output power to DC power consumption.                                         |

| Power-Added Efficiency (PAE) | Ratio of the difference between output power and input power to DC power consumption      |

| Phase Noise (PN)             | Measure of oscillator stability represented in the frequency domain at a specified offset |

| Voltage Swing (VSwg)         | Maximum peak voltage level achievable at the output node                                  |

The CSLNA is valued for its simplicity and favorable gain—noise trade-off, especially when paired with inductive source degeneration [30]. The CGLNA, often used in ultra-wideband systems, enables broadband input matching but typically suffers from a higher noise figure [32]. The CLNA improves gain—bandwidth product and reverse isolation, making it ideal for high-frequency, high-linearity applications [33]. The DLNA exploits circuit symmetry to enhance linearity and reject common-mode noise, and is commonly found in high-performance RF front-end designs [34]. The design parameters and performance metrics associated with these topologies are summarized in Table 6.

Figure 7: Schematic diagrams of the four LNA topologies.

Table 6: LNA topologies with parameter sweep ranges, sample sizes, and performance metrics.

| Dataset Type | Topology (Code) | # of Samples | Parameter                                                                            | Sweep Range                                                                                           | Performance Metrics (Unit)              |

|--------------|-----------------|--------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------|

|              | CGLNA (0)       | 52k          | $\begin{array}{c c} C_1 \\ C_2 \\ C_b \\ L_d \\ L_s \\ W_N \end{array}$              | [100–600] fF<br>[50–300] fF<br>[250–750] fF<br>[80–580] pH<br>[0.5–5.5] nH<br>[12–23] µm              |                                         |

| LNA          | CLNA (1)        | 62k          | $ \begin{array}{c c} C_1, C_2 \\ L_d \\ L_g \\ L_s \\ W_{N1} \\ W_{N2} \end{array} $ | [50–250] fF<br>[140–300] pH<br>[0.4–2] nH<br>[50–250] pH<br>[3–5] µm<br>[7–9] µm                      | DCP (W) PGain (dB) S <sub>11</sub> (dB) |

|              | CSLNA (2)       | 39k          | $\begin{array}{c c} C \\ L_g \\ L_s \\ W_N \\ V_{gs} \end{array}$                    | [100–300] fF<br>[4–6] nH<br>[100–200] pH<br>[2.5–4] µm<br>[0.5–0.9] V                                 | NF (dB)<br>BW (Hz)                      |

|              | DLNA (3)        | 92k          | $\begin{array}{c c} C_1 \\ C_2 \\ L_d \\ L_g \\ L_s \\ W_{N1} \\ W_{N2} \end{array}$ | [100–190] fF<br>[130–220] fF<br>[100–250] pH<br>[600–900] pH<br>[50–80] pH<br>[4–9.4] µm<br>[5–14] µm |                                         |

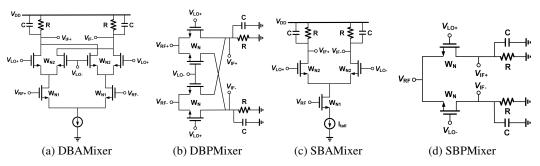

#### **B.2** Mixers

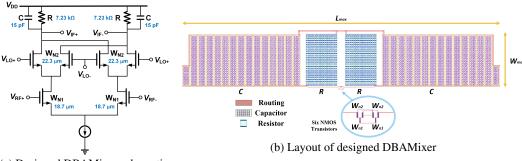

Mixers are fundamental nonlinear components in RF systems, responsible for frequency translation by combining two input signals to produce outputs at the sum and difference of their frequencies. This functionality is essential for transferring signals across frequency domains and is widely used in both transmission and reception paths [35]. To capture diverse mixer architectures, we implement four representative topologies in this work—double-balanced active mixer (DBAMixer), double-balanced passive mixer (DBPMixer), single-balanced active mixer (SBAMixer), and single-balanced passive mixer (SBPMixer)—as shown in Figure 8.

The DBAMixer integrates amplification and differential switching to achieve conversion gain and high port-to-port isolation. Despite its elevated power consumption and design complexity, it is well suited for systems requiring robust performance over varying conditions [36]. The DBPMixer features a fully differential structure that suppresses signal leakage and improves isolation, at the cost of signal loss and a strong local oscillator drive requirement [37]. The SBAMixer includes an amplification stage preceding the switching core to enhance signal strength and reduce noise, offering a balanced performance trade-off with increased power consumption and limited spurious rejection [30]. The SBPMixer employs a minimalist switching structure to perform frequency translation without active gain, enabling low power operation in applications with relaxed performance demands [38]. The parameters and performance metrics for these mixer topologies are listed in Table 7.

Figure 8: Schematic diagrams of the four Mixer topologies.

Table 7: Mixer topologies with parameter sweep ranges, sample sizes, and performance metrics.

| Dataset Type | Topology (Code) | # of Samples | Parameter                                                                             | Sweep Range                                                                                                                                                                | Performance Metrics (Unit) |

|--------------|-----------------|--------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|              | DBAMixer (4)    | 42k          | $\begin{bmatrix} & C \\ R \\ W_{N1} \\ W_{N2} \end{bmatrix}$                          | [1–10] pF<br>[1–10] kΩ<br>[10–30] μm<br>[5–25] μm                                                                                                                          |                            |

| Mixer        | DBPMixer (5)    | 42k          | C<br>R<br>W <sub>N</sub>                                                              | [100–500] fF<br>[100–600] Ω<br>[10–30] μm                                                                                                                                  | DCP (W)<br>CGain (dB)      |

|              | SBAMixer (6)    | 52k          | $ \left  \begin{array}{c} C \\ R \\ W_{N1} \\ W_{N2} \\ I_{tail} \end{array} \right $ | $ \begin{array}{c} [1 - 15]  \mathrm{pF} \\ [0.7 - 2.1]  \mathrm{k}\Omega \\ [10 - 30]  \mathrm{\mu m} \\ [10 - 20]  \mathrm{\mu m} \\ [3 - 10]  \mathrm{mA} \end{array} $ | NF (dB)<br>VSwg (V)        |

|              | SBPMixer (7)    | 44k          | C<br>R<br>W <sub>N</sub>                                                              | [1–30] pF<br>[1–30] kΩ<br>[5–29.5] μm                                                                                                                                      |                            |

#### **B.3** Power Amplifiers (PAs)

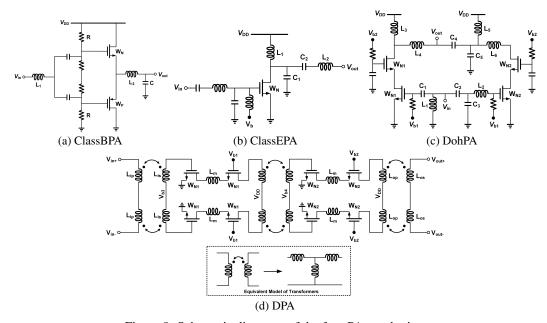

Power amplifiers (PAs) are the most power-intensive components in radio-frequency (RF) systems and serve as the final interface between transceiver electronics and the antenna. Given their widespread use and the stringent demands of modern communication standards, PA design requires careful trade-offs across key performance metrics [39]. Based on the transistor operating mode, PAs are typically grouped into several canonical classes [40]. In this work, we implement four representative topologies—Class-B PA (ClassBPA), Class-E PA (ClassEPA), Doherty PA (DohPA), and differential PA (DPA)—as shown in Figure 9.

The ClassBPA employs complementary transistors to deliver high gain with moderate efficiency, making it suitable for linear amplification scenarios [41]. The ClassEPA uses a single transistor configured as a switch, paired with a matching network. By minimizing the overlap between drain voltage and current, this topology enables high-efficiency operation and improved robustness to component variation [30]. The DohPA combines main and peaking amplifiers using symmetric two-stack transistors, maintaining consistent gain and efficiency under varying power levels [42]. The DPA features a two-stage cascode structure designed to maximize gain and linearity, offering a favorable trade-off between output power and power consumption [43]. For this topology, we replace the transformer with a T-equivalent network to simplify modeling and training of the graph neural network. Parameter sweeps and performance metrics for these PAs are listed in Table 8.

Figure 9: Schematic diagrams of the four PA topologies.

Table 8: PA topologies with parameter sweep ranges, sample sizes, and performance metrics.

| ·   | Dataset Type | Topology (Code)            | # of Samples | Parameter                                                                                        | Sweep Range                                                                                                                                           | Performance Metrics (Unit)                                                                  |

|-----|--------------|----------------------------|--------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|     |              | ClassBPA (8)  ClassEPA (9) | 35k<br>46k   | $\begin{array}{c} C \\ L_1 \\ L_2 \\ R \\ W_N \\ W_P \\ \end{array}$                             | [55–205] fF<br>[1–1.4] nH<br>[1–8.5] pH<br>[1.5–4] kΩ<br>[10–20] μm<br>[3–8] μm<br>[100–200] fF<br>[500–700] fF<br>[100–300] pH                       | DCP (W)                                                                                     |

|     |              |                            |              | $egin{array}{c} L_2 \ W_N \end{array}$                                                           | [100–150] pH<br>[15–30] μm                                                                                                                            | PGain (dB)                                                                                  |

| 529 | PA           | DohPA (10)                 | 120k         | $C_1\\C_2\\C_3,C_5\\C_4\\L_1,L_5\\L_2\\L_3\\L_4\\L_6\\W_{N1},W_{N2}$                             | [2–3] pF<br>[200–300] fF<br>[100–200] fF<br>[300–400] fF<br>[100–200] pH<br>[350–450] pH<br>[500–600] pH<br>[150–250] pH<br>[300–400] pH<br>[6–13] µm | S <sub>11</sub> (dB)<br>S <sub>22</sub> (dB)<br>P <sub>SAT</sub> (dBm)<br>DE (%)<br>PAE (%) |

|     |              | DPA (11)                   | 80k          | $\begin{array}{c} L_{ip} \\ L_{is} \\ L_{op} \\ L_{os} \\ L_{m} \\ W_{N1} \\ W_{N2} \end{array}$ | [100–500] pH<br>[300–700] pH<br>[0.8–1.2] nH<br>[400–800] pH<br>[50–250] pH<br>[6–31] µm<br>[10–35] µm                                                |                                                                                             |

#### **B.4** Voltage Amplifiers (VAs)

Voltage amplifiers (VAs) are fundamental components in analog circuit design, responsible for increasing signal amplitude while preserving waveform integrity. Effective VA design requires balancing key performance metrics tailored to both RF and baseband operating conditions [44]. In this work, we implement four widely used VA topologies—common-source VA (CSVA), commongate VA (CGVA), cascode VA (CVA), and source follower VA (SFVA)—as shown in Figure 10.

The CSVA remains the most widely adopted configuration due to its structural simplicity and high voltage gain. It is frequently used as the first gain stage in various analog systems [45]. The CGVA is suitable for applications requiring low input impedance and wide bandwidth, such as impedance transformation or broadband input matching [46]. The CVA, which cascades a common-source stage with a common-gate transistor, improves the gain—bandwidth product and enhances stability, making it ideal for applications demanding wide dynamic range and robust gain control [47]. The SFVA, also known as a common-drain amplifier, provides near-unity voltage gain and low output impedance, making it well suited for interstage buffering, load driving, and impedance bridging [48]. Parameter ranges and performance specifications for these VA topologies are listed in Table 9.

Figure 10: Schematic diagrams of the four VA topologies.

Table 9: VA topologies with parameter sweep ranges, sample sizes, and performance metrics.

| Dataset Type | Topology (Code) | # of Samples | Parameter                                                                       | Sweep Range                                                                                                                      | Performance Metrics (Unit) |  |  |  |  |

|--------------|-----------------|--------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|

|              | CGVA (12)       | 33k          | $\left \begin{array}{c} C \\ R \\ W_{N1} \\ W_{N2} \end{array}\right $          | $ \begin{bmatrix} [0.11.5] \text{ pF} \\ [0.11.5] \text{ k}\Omega \\ [530]  \mu\text{m} \\ [510]  \mu\text{m} \\ \end{bmatrix} $ |                            |  |  |  |  |

| VA           | CSVA (13)       | 21k          | $\left \begin{array}{c} R \\ W_N \\ V_{DD} \\ V_{gate} \end{array}\right $      | [0.7–1.5] kΩ<br>[3–15] μm<br>[1–1.8] V<br>[0.6–0.9] V                                                                            | DCP (W)<br>VGain (dB)      |  |  |  |  |

|              | CVA (14)        | 22k          | $\left \begin{array}{c} R \\ W_{N1}, W_{N2} \\ W_{N3} \end{array}\right $       | [1–3] kΩ<br>[1–10] μm<br>[10–15] μm                                                                                              | BW (Hz)                    |  |  |  |  |

|              | SFVA (15)       | 28k          | $ \begin{vmatrix} W_{N1} \\ W_{N2} \\ V_{DD} \\ V_{gate} \\ V_b \end{vmatrix} $ | [40–60] μm<br>[2–8] μm<br>[1.1–1.8] V<br>[0.6–1.2] V<br>[0.5–0.9] V                                                              |                            |  |  |  |  |

## **B.5** Voltage-Controlled Oscillators (VCOs)

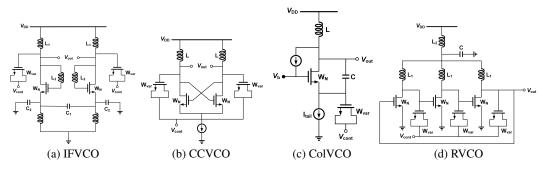

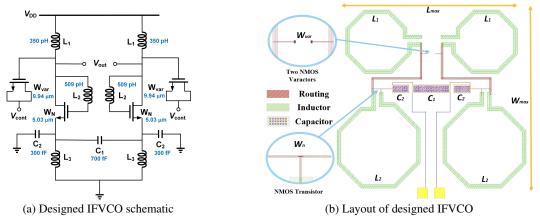

Voltage-controlled oscillators (VCOs) are essential building blocks in analog and RF systems, responsible for generating periodic waveforms with frequencies modulated by a control voltage. These circuits rely on amplification, feedback, and resonance to sustain stable oscillations. Owing to their wide tuning range, low power consumption, and ease of integration, VCOs are broadly used in systems such as phase-locked loops (PLLs), frequency synthesizers, and clock recovery circuits [49]. In this work, we implement four representative VCO topologies—inductive-feedback VCO (IFVCO), cross-coupled VCO (CCVCO), Colpitts VCO (ColVCO), and ring VCO (RVCO)—as shown in Figure 11.

The IFVCO employs an NMOS differential pair with an inductor-based feedback path to sustain oscillations. This topology provides favorable noise performance and compact layout, making it well suited for low-voltage, low-power designs [50]. The CCVCO achieves negative resistance through cross-coupling, enabling low phase noise and high integration density, and is widely adopted in frequency synthesizers and PLLs [51]. The ColVCO uses an LC tank and capacitive feedback to achieve high frequency stability and low phase noise, making it ideal for precision RF communication and instrumentation [52]. The RVCO consists of cascaded delay stages forming a feedback loop, offering low power consumption, wide tuning range, and minimal area footprint, though at the cost of higher phase noise. It is commonly used in on-chip clock generation and low-power sensor applications [53]. Design parameters and performance metrics for these VCO topologies are presented in Table 10.

Figure 11: Schematic diagrams of the four VCO topologies.

Table 10: VCO topologies with parameter sweep ranges, sample sizes, and performance metrics.

| Dataset Type | Topology (Code) | # of Samples | Parameter                                                                             | Sweep Range                                                                        | Performance Metrics (Unit)     |

|--------------|-----------------|--------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------|

|              | IFVCO (16)      | 43k          | $\begin{array}{ c c } & C_1 \\ & C_2 \\ & L_1 \\ & L_2 \\ & W_N, W_{var} \end{array}$ | [700–900] fF<br>[50–250] fF<br>[400–600] pH<br>[500–700] pH<br>[5–9] μm            |                                |

|              | CCVCO (17)      | 54k          | $\left \begin{array}{c} L \\ W_N \\ W_{var} \end{array}\right $                       | [200–400] pH<br>[10–35] μm<br>[5–30] μm                                            | DCP (W)<br>OscF (Hz)           |

| VCO          | ColVCO (18)     | 90k          | $\begin{matrix} C \\ L \\ W_N \\ W_{var} \\ V_b \\ I_{tail} \end{matrix}$             | [80–140] fF<br>[250–350] pH<br>[30–50] µm<br>[5–15] µm<br>[0.7–1.2] V<br>[5–15] mA | TR (Hz) OutP (dBm) PN (dBc/Hz) |

|              | RVCO (19)       | 46k          | $\begin{array}{ c c } & C \\ & L_1 \\ & L_2 \\ & W_N \\ & W_{var} \end{array}$        | [300–700] fF<br>[300–500] pH<br>[50–250] pH<br>[20–40] µm<br>[5–25] µm             |                                |

## C Graph-Based Circuit Representation

To enable GNN-based modeling of analog circuits, we represent each netlist as a directed multigraph where nodes correspond to electrical nets and edges encode circuit components such as transistors, capacitors, inductors, and voltage sources. Each edge is labeled with its component type and terminal role (e.g., gate, source, drain), and component-specific attributes are stored as edge features. For transistors, labels such as GS, DS, and DG denote source-to-gate, drain-to-source, and drain-to-gate connections, respectively.

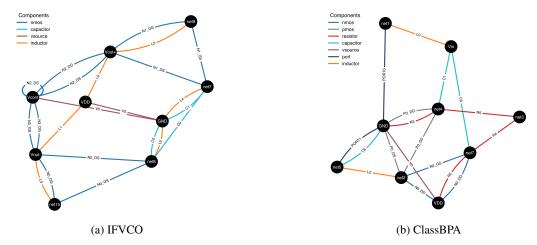

Figure 12 illustrates two representative graph structures extracted from our dataset: an IFVCO and a ClassBPA. The visual encoding highlights the diversity of components and connectivity patterns across topologies. Edges corresponding to the same component type share a common color for visual consistency and semantic clarity. These structured graphs serve as the primary input to our GNN pipeline for performance prediction and inverse design.

Figure 12: Graph representations of two analog circuit topologies from our dataset: (a) IFVCO and (b) ClassBPA. Nodes represent electrical nets, and colored edges denote circuit components such as transistors, capacitors, inductors, and sources. Each component type is visually distinguished by color and labeled with its name and terminal role (e.g., N2\_GS, V0). These graphs serve as input to our GNN-based performance modeling and inverse design pipeline.

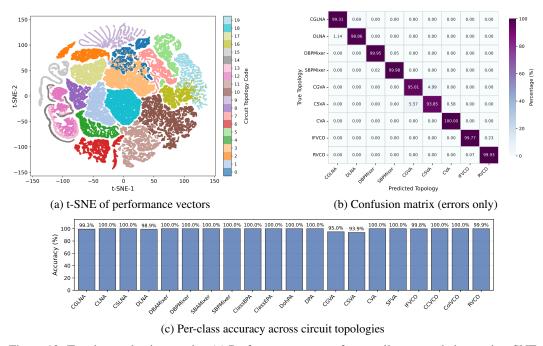

Figure 13: Topology selection results. (a) Performance vectors form well-separated clusters in t-SNE space, showing that circuit functionality is semantically predictive of topology. (b) Misclassifications primarily occur among voltage amplifier variants with overlapping gain-bandwidth tradeoffs. (c) Per-class test accuracy exceeds 93% across all 20 circuit topologies.

## D Additional Results for Performance-Driven Topology Selection

To further analyze the topology classification stage, we visualize the learned input representation and per-class performance. Normalized performance vectors encode rich semantic information about circuit behavior. When projected into a two-dimensional t-SNE space [63] (Figure 13(a)), the resulting clusters align closely with topology labels, indicating that performance specifications reflect underlying schematic structure and are effective inputs for supervised classification.