# Tiled Flash Linear Attention: More Efficient Linear RNN and xLSTM Kernels

Maximilian Beck<sup>1,2</sup> Korbinian Pöppel<sup>1,2</sup> Phillip Lippe<sup>2\*</sup> Sepp Hochreiter<sup>1,2</sup>

<sup>1</sup> ELLIS Unit, LIT AI Lab, Institute for Machine Learning, JKU Linz, Austria

<sup>2</sup> NXAI GmbH, Linz, Austria

#### **Abstract**

Linear RNNs with gating recently demonstrated competitive performance compared to Transformers in language modeling. Although their linear compute scaling in sequence length offers theoretical runtime advantages over Transformers, realizing these benefits in practice requires optimized custom kernels, as Transformers rely on the highly efficient Flash Attention kernels (Dao, 2024). Leveraging the chunkwise-parallel formulation of linear RNNs, Flash Linear Attention (FLA) (Yang & Zhang, 2024) shows that linear RNN kernels are faster than Flash Attention, by parallelizing over chunks of the input sequence. However, since the chunk size of FLA is limited, many intermediate states must be materialized in GPU memory. This leads to low arithmetic intensity and causes high memory consumption and IO cost, especially for long-context pre-training. In this work, we present Tiled Flash Linear Attention (TFLA), a novel kernel algorithm for linear RNNs, that enables arbitrary large chunk sizes and high arithmetic intensity by introducing an additional level of sequence parallelization within each chunk. First, we apply TFLA to the xLSTM with matrix memory, the mLSTM (Beck et al., 2024). Second, we propose an mLSTM variant with sigmoid input gate and reduced computation for even faster kernel runtimes at equal language modeling performance. In our speed benchmarks, we show that our new mLSTM kernels based on TFLA outperform highly optimized Flash Attention, Linear Attention and Mamba kernels, setting a new state of the art for efficient long-context sequence modeling primitives. Our code is available at: https://github.com/NX-AI/mlstm\_kernels

#### 1 Introduction

With the trend of training models of ever increasing size with large datasets on thousands of GPUs, it becomes increasingly important to optimize the model architecture as well as its low-level implementations for modern hardware. Transformers (Vaswani et al., 2017), which are the core architecture of nowadays state-of-the-art models are highly optimized, but the computational requirements of self-attention scale quadratically with sequence length. This creates significant challenges for both training and inference on long context.

Recently, recurrent alternatives with linear scaling in sequence length (Beck et al., 2024; Sun et al., 2023; Dao & Gu, 2024; Yang et al., 2024b) promise efficiency gains, especially on long sequences and during inference while providing competitive performance. The success of these emerging recurrent architectures is based on two main pillars: (1) A parallel or chunkwise-parallel formulation (Sun et al., 2023; Hua et al., 2022), which, like Attention, calculates all outputs in parallel during training, and (2) kernel implementations that are close to or exceed training speeds of FlashAttention (Dao, 2024).

Yang et al. (2024b) show that their custom FlashLinearAttention (FLA) kernels, based on the <a href="https://example.chunkwise-parallel-formulation.of">https://example.chunkwise-parallel-formulation.of</a> linear RNNs, achieve faster runtimes than FlashAttention.

\*Now at Google Deepmind.

now at Google Beeplinia.

They accomplish this by dividing the sequence into chunks and recurrently materializing only the initial RNN state of each chunk in GPU memory. Subsequently, in the parallel part they employ one level of sequence parallelism and compute the outputs for each chunk in parallel. For a small chunk size and long sequences, this leads to a large amount of intermediate states to be stored and loaded from GPU memory, which increases memory consumptionand decreases arithmetic intensity. Since modern GPUs see a faster increase in computation throughput than memory bandwidth (Gholami et al., 2024), it is essential to minimize large memory IO and increase arithmetic intensity. A simple approach would be to increase the chunk size. However, the chunk size of FLA is limited by the physical SRAM available on the GPU.

To solve this problem, we introduce *Tiled Flash Linear Attention* (TFLA) which enables unlimited chunk sizes by introducing a second level of sequence parallelism via tiling of the matrix computations in sequence dimension within each chunk. This increases the arithmetic intensity of the kernels and allows us to efficiently balance memory consumption and IO vs. computation.

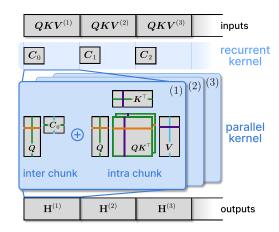

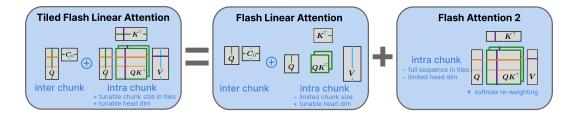

Figure 1: **Tiled Flash Linear Attention (TFLA)** consists of a recurrent kernel and a parallel kernel, which process the input sequence in chunks  $QKV^{(k)}$  (1st level of sequence parallelism). The recurrent kernel materializes the memory state  $C_{k-1}$  for each chunk. The parallel kernel computes the output states  $\mathbf{H}^{(k)}$  for all chunks. TFLA uses tiling for the 3 matrix-multiplications in the parallel kernel (2nd level of sequence parallelism) to fully utilize the hardware and to prevent materialization of many memory states.

In this paper, we implement our Tiled Flash Linear Attention algorithm for the xLSTM with matrix memory – the mLSTM Beck et al. (2024). The mLSTM is a linear RNN that uses exponential gating with scalar gates per head, along with an additional normalizer state for output normalization. This gating mechanism has demonstrated competitive performance compared to Transformers and Mamba on language modeling tasks at moderate scales. However, for comparisons at even larger scales, efficient kernels that leverage the chunkwise-parallel formulation for the mLSTM were still missing. In our speed benchmarks, we show that our new mLSTM kernels based on TFLA outperform highly optimized Attention, Linear Attention and Mamba kernels.

After optimizing our kernels for the existing mLSTM computation, we seek ways to reduce kernel runtime by targeted modifications to the mLSTM. Towards this end, we propose *mLSTMsig*, an mLSTM with sigmoid input gate and reduced computation, that enables even faster kernel implementations at no performance drops on language modeling up to 1.4B parameter scale.

Finally, motivated by the equal performance of both mLSTM variants, we perform an empirical study inspired by transfer function analysis from control theory (Ogata, 2010) to understand their differences and characteristics. We find that both mLSTM variants exhibit the same transfer behavior and, moreover, our analysis suggests that the input gate biases should be initialized at larger negative values. In extensive experiments on language modeling, we confirm that this initialization improves training stability as well as the overall performance of mLSTM models.

To summarize, in this work, we make the following contributions: (1) We introduce *Tiled Flash Linear Attention*, a new chunkwise-parallel kernel algorithm for Linear RNNs with two levels of sequence parallelism, that enables arbitrary large chunk sizes and apply it to the mLSTM (Beck et al., 2024). (2) We introduce *mLSTMsig*, a faster mLSTM variant with sigmoid input gate with no performance losses up to 1.4B parameter scales. (3) We improve the training stability and performance of the mLSTM through careful gate initialization guided by our empirical transfer behavior analysis.

#### 2 mLSTM Formulations

The mLSTM cell is the fully parallelizable part of the xLSTM (Beck et al., 2024). It has a matrix memory and exponential gating.

#### **Recurrent Formulation**

In its recurrent formulation, the mLSTM cell processes the series of input vectors  $x_t \in \mathbb{R}^d$  for time steps  $t \in \{1, \dots, T\}$  mapping a state  $(\boldsymbol{h}_{t-1}, \boldsymbol{C}_{t-1}, \boldsymbol{n}_{t-1}, m_{t-1})$  to a successor state  $(\boldsymbol{h}_t, \boldsymbol{C}_t, \boldsymbol{n}_t, m_t)$ given an input  $x_t$ . Here,  $h_t \in \mathbb{R}^{d_{hv}}$  denotes the hidden state,  $C_t \in \mathbb{R}^{d_{qk} \times d_{hv}}$  denotes the cell state responsible for long-term memory,  $n_t \in \mathbb{R}^{d_{qk}}$  denotes the normalizer state, and  $m_t \in \mathbb{R}$  denotes the max state. Together normalizer and max state control the magnitude of the exponential input gate and ensure stability (see Appendix D.1). The recurrent mLSTM formulation is given by the following state update equations:

$$m_t = \max\left\{\log\sigma(\tilde{\mathbf{f}}_t) + m_{t-1}, \ \tilde{\mathbf{i}}_t\right\}$$

(1)

$$C_t = f_t C_{t-1} + i_t k_t v_t^{\top}$$

(2)

$$\boldsymbol{n}_t = f_t \, \boldsymbol{n}_{t-1} + i_t \, \boldsymbol{k}_t \tag{3}$$

$$\widetilde{\boldsymbol{h}}_{t} = \frac{\boldsymbol{C}_{t}^{\top} \left( \boldsymbol{q}_{t} / \sqrt{d_{qk}} \right)}{\max \left\{ \left| \boldsymbol{n}_{t}^{\top} \left( \boldsymbol{q}_{t} / \sqrt{d_{qk}} \right) \right|, \exp(-m_{t}) \right\}}$$

(4)

$$\mathbf{h}_t = \mathbf{o}_t \odot \text{NORM}(\widetilde{\mathbf{h}}_t)$$

(5)

The scalar forget and input gates  $i_t, f_t \in \mathbb{R}$  are computed as  $f_t = \exp\left(\log \sigma(\tilde{f}_t) + m_{t-1} - m_t\right)$  and  $\mathbf{i}_t = \exp(\tilde{\mathbf{i}}_t - m_t)$  with the pre-activations  $\{\tilde{\mathbf{i}}_t, \tilde{\mathbf{f}}_t\} = \mathbf{w}_{\{\mathbf{i}, f\}}^{\top} \mathbf{x}_t + \hat{b}_{\{\mathbf{i}, f\}}$ , respectively. The vector output gate  $\mathbf{o}_t \in \mathbb{R}^{d_{hv}}$  is given by  $\mathbf{o}_t = \sigma\left(\tilde{\mathbf{o}}_t\right)$  with the pre-activations  $\tilde{\mathbf{o}}_t = \mathbf{W}_{\mathbf{o}} \mathbf{x}_t + \mathbf{b}_{\mathbf{o}}$  and the sigmoid function  $\sigma$ . The norm layer NORM in (5) can be either RMS norm (Zhang & Sennrich, 2019) or LayerNorm (Ba et al., 2016). Typically, multiple of these cells operate simultaneously as parallel heads, similar to Transformers (Vaswani et al., 2017).

#### **Chunkwise-Parallel Formulation**

The chunkwise-parallel formulation is a trade-off between the parallel and the fully recurrent formulation. It has a recurrent part and a (quadratic) parallel part, with an overall sub-quadratic scaling in sequence length. Similar to the fully parallel formulation (see Appendix B.1), we assume that all inputs are available at once. We then split the sequence of length T into  $N_c = \lceil T/L \rceil$  chunks of length L and use  $k \in \{1, \dots, N_c\}$  for the chunk index. We rearrange the input and forget gates, as well as the queries, keys, and values into chunkwise matrices, where the chunk index becomes the first dimension. For example, the forget gate pre-activations  $\tilde{\mathbf{f}} \in \mathbb{R}^T$  are rearranged into a matrix  $\tilde{\mathbf{f}} = (\tilde{\mathbf{f}}^{(1)}, \tilde{\mathbf{f}}^{(2)}, \dots, \tilde{\mathbf{f}}^{(N_c)}) \in \mathbb{R}^{N_c \times L}, \text{ where each row } \tilde{\mathbf{f}}^{(k)} = (\mathbf{f}_{(k-1)N_c+1}, \mathbf{f}_{(k-1)N_c+2}, \dots, \mathbf{f}_{kN_c}) \in$  $\mathbb{R}^L$  contains the pre-activations of the chunk k. The input gate pre-activations follow analogously. Similarly, the queries, keys and values are rearranged into chunkwise tensors  $Q, K \in \mathbb{R}^{N_c \times L \times d_{qk}}$ and  $V \in \mathbb{R}^{N_c imes L imes d_{hv}}$ . Here, the query matrix  $Q^{(k)} = (q_{(k-1)N_c+1}, \dots, q_{kN_c}) \in \mathbb{R}^{L imes d_{qk}}$  contains the query vectors of chunk k. Keys, and values follow analogously. For notational simplicity we drop the leading  $N_c$  dimension and omit normalization layer and the output gate, i.e. consider  $h_t$  as hidden state outputs.

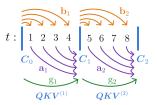

**Chunkwise Gates.** Given the logarithmic forget gates  $\bar{\mathbf{f}}^{(k)} =$  $\log \sigma(\tilde{\mathbf{f}}^{(k)}) \in \mathbb{R}^L$  and input gates  $\tilde{\mathbf{i}}^{(k)} = \log \exp(\tilde{\mathbf{i}}^{(k)}) \in \mathbb{R}^L$ ,  $t: \begin{bmatrix} 1 & 2 & 3 & 4 \\ we can compute the logarithmic chunkwise gates <math>g_k \in \mathbb{R}$ , and  $\mathbf{b}_k, \mathbf{a}_k \in \mathbb{R}^L$  as  $g_k = \sup \left(\bar{\mathbf{f}}^{(k)}\right)$ ,  $\mathbf{b}_k = \operatorname{cumsum}\left(\bar{\mathbf{f}}^{(k)}\right)$ , and  $\mathbf{a}_k = \text{rev\_cumsum}\left(\mathbf{\bar{f}}^{(k)}\right) + \mathbf{\bar{i}}^{(k)}$ . We refer to Appendix B.2 for more details on the chunkwise gates. In Figure 2, we show the summed forget gates  $g_k$  contain the forget gate contribution of all forget gates within a chunk. The cumulative forget gate vectors  $\mathbf{b}_k$  contain the forget gate contributions from the beginning of the chunk up to the current time step within the current chunk. The cumulative input gate vectors  $\mathbf{a}_k$ contain the input gates for every timestep as well as the forget gate contributions from the current time step to the end of the chunk.

Figure 2: Illustration of the chunkwise gates  $\mathbf{a}_k$ ,  $\mathbf{b}_k$ and  $g_k$  with chunk size L=4. Each arrow denotes an element in the gate vectors. See Figure 9 in Appendix B.2 for more details.

**Inter-chunk Recurrent Contribution.** The inter-chunk recurrence is given by

$$C_k = \bar{\mathbf{g}}_k C_{k-1} + \left(\bar{\mathbf{a}}_k \odot \mathbf{K}^{(k)}\right)^{\top} \mathbf{V}^{(k)}$$

(6)

$$n_k = \bar{\mathbf{g}}_k n_{k-1} + \left(\bar{\mathbf{a}}_k \odot \mathbf{K}^{(k)}\right)^{\top} \mathbf{1},$$

(7)

where  $\bar{g}_k$  and  $\bar{a}_k$  are the stabilized chunkwise gates. This recurrent part resembles the fully recurrent formulation in Section 2.1, but instead of computing the intermediate states for every timestep t, we compute them directly for every L time steps without materializing the states in between.

Intra-chunk Parallel Contribution. The recurrent part is followed by the intra-chunk parallel contribution:

$$\widetilde{\mathbf{D}}^{(k)} = \begin{cases} -\infty & \text{for } i < j \\ \mathbf{b}_k - \mathbf{b}_k^{\top} + \overline{\mathbf{i}}^{(k)}^{\top} & \text{for } i \geqslant j \end{cases}$$

$$\overline{\mathbf{S}}^{(k)} = \left(\frac{1}{\sqrt{d_{qk}}} \mathbf{Q}^{(k)} \mathbf{K}^{(k)}^{\top}\right) \odot \mathbf{D}^{(k)} = \mathbf{S}^{(k)} \odot \mathbf{D}^{(k)},$$

(9)

$$\overline{\mathbf{S}}^{(k)} = \left(\frac{1}{\sqrt{d_{qk}}} \mathbf{Q}^{(k)} \mathbf{K}^{(k)}^{\top}\right) \odot \mathbf{D}^{(k)} = \mathbf{S}^{(k)} \odot \mathbf{D}^{(k)}, \tag{9}$$

where  $\mathbf{D}^{(k)} \in \mathbb{R}^{L \times L}$  is the stabilized gate matrix. Compared to the fully parallel part from Appendix B.1, the quadratic cost of the matrices  $\mathbf{D}^{(k)}, \mathbf{S}^{(k)} \in \mathbb{R}^{L \times L}$  is greatly reduced, since the chunk size L is typically small compared to the sequence length T.

**Output Computation.** Finally, the contributions from the intra-chunk parallel part  $\mathbf{H}_{\text{intra}}^{(k)}$  are combined with the inter-chunk recurrent part  $\mathbf{H}_{\text{inter}}^{(k)}$  to obtain the hidden states  $\mathbf{H}^{(k)} \in \mathbb{R}^{L \times d_{hv}}$  for each chunk k (see Figure 1):

$$\mathbf{H}_{\text{inter}}^{(k)} = \left(\overline{\mathbf{b}}_k \odot \frac{\mathbf{Q}^{(k)}}{\sqrt{d_{qk}}}\right) \mathbf{C}_{k-1} = \overline{\mathbf{Q}}^{(k)} \mathbf{C}_{k-1}, \qquad \mathbf{H}_{\text{intra}}^{(k)} = \overline{\mathbf{S}}^{(k)} \mathbf{V}^{(k)}, \tag{10}$$

$$\mathbf{H}^{(k)} = \left(\mathbf{H}_{\text{inter}}^{(k)} + \mathbf{H}_{\text{intra}}^{(k)}\right) / \mathbf{h}_{\text{denom}}^{(k)}, \tag{11}$$

where  $\mathbf{h}_{\text{denom}}^{(k)} \in \mathbb{R}^L$  is a normalization factor. Appendix B.2 and B.3 provide a detailed description of the chunkwise-parallel forward and backward pass. Appendix F provides the FLOP and memory operation counts for all formulations.

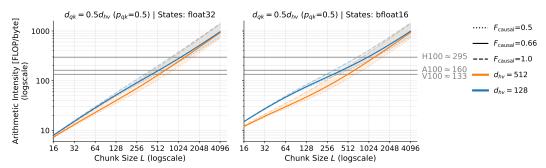

#### 3 **Tiled Flash Linear Attention**

FlashLinearAttention (Yang et al., 2024b) introduces a fast kernel algorithm for the chunkwise formulation for Linear Attention (cf. Section 2.2 without gates) and shows that their implementation is faster than optimized FlashAttention Dao (2024). This speedup is achieved by single level sequence parallelism, where the states  $C_k$  are first materialized in GPU memory and then the outputs  $\mathbf{H}^{(k)}$  are computed in parallel. However, since in FlashLinearAttention the chunk size parameter determines the tile sizes in SRAM, the maximum chunk size is limited (typically L=64) by the physical SRAM size of the GPU. Therefore, we have to materialize many states in HBM, where the number of states is  $N_c = \lceil T/L \rceil$ . This leads to low arithmetic intensity and high GPU memory consumption, which poses challenges especially for long-context pre-training.

We begin with a brief review of fundamentals on GPUs for writing efficient kernels in Appendix C.1.

More Efficient Kernels via Two Level Sequence Parallelism. To address the issue of limited chunk sizes, Tiled Flash Linear Attention (TFLA) introduces two levels of sequence parallelism, which enables fast kernels and a trade-off between memory consumption and computational efficiency (see Figure 6). The first level is the parallelization over the chunks of the sequence, which requires to compute and materialize intermediate states  $C_k$  in GPU High Bandwidth memory (HBM). For this we use a recurrent kernel similar to previous work (Yang et al., 2024b). The second level is the parallelization within each chunk, which is achieved by tiling the intra chunk attention matrix along the chunk dimension. This second level of parallelism enables large chunk sizes and hence reduces the memory consumption for the intermediate states as we have to store and load  $N_c = \lceil T/L \rceil$ intermediate states in HBM on each kernel call, where T is the sequence length and L is the chunk size. In addition to the two levels of sequence parallelism and the naive parallelization over the batch

and head dimensions, TFLA also parallelizes over the embedding dimension. This enables arbitrary large head dimensions and results in a massive parallelization over five dimensions, which is crucial for achieving high performance on modern GPUs. We analyze the theoretical runtime of our TFLA kernels in Appendix G.

**Forward Pass.** We review the matrix multiplication operations of the intra-chunk parallel part of the mLSTM in order to show how we efficiently parallelize these operations. For simplicity we omit the the gate computations and normalization, as these do not influence the work partitioning. We also omit the leading batch, head and chunk dimension, over which we can parallelize naively as they do not interact with the matrix multiplication (see Table 1). In simplified form, the intra-chunk parallel forward pass of the mLSTM (and other linear RNNs) for a chunk k can be written as three matrix multiplications, which we fuse into a single kernel:

$$\mathbf{H}^{(k)}_{(L_{hq} \times d_{hv})} = \underbrace{\begin{pmatrix} \mathbf{Q}^{(k)} & \mathbf{K}^{(k)}^{\top} \\ (L_{hq} \times d_{qk}) & (d_{qk} \times L_{kv}) \end{pmatrix} \mathbf{V}^{(k)}_{(L_{kv} \times d_{hv})}}_{\mathbf{H}^{(k)}} + \underbrace{\begin{pmatrix} \mathbf{Q}^{(k)} & \mathbf{C}_{k-1} \\ (L_{hq} \times d_{qk}) & (d_{qk} \times d_{hv}) \end{pmatrix}}_{\mathbf{H}^{(k)}}$$

(12)

In Appendix A.2, we show that TFLA can be applied to any linear RNN that either follows or can be reformulated into this form. In order to parallelize the computation in (12), we introduce the block sizes  $B_{Lhq}$ ,  $B_{Lkv}$ ,  $B_{dqk}$  and  $B_{dhv}$  for the attention matrix, query, key, value and hidden state dimensions  $L_{hq}$ ,  $L_{kv}$ ,  $d_{qk}$  and  $d_{hv}$ , along which we either parallelize or accumulate by using a loop inside the kernel.

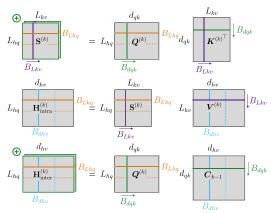

In Figure 3, we show our TFLA tiling strategy for the forward pass  $\mathbf{H}^{(k)}$  kernel. We parallelize across the outer sequence dimension  $L_{hq}$  with  $N_{Lhq} = L_{hq}/B_{Lhq}$  programs, and across the outer embedding dimension  $d_{hv}$  with  $N_{dhv} = d_{hv}/B_{dhv}$  programs. We loop over the inner dimensions  $L_{kv}$  and  $d_{qk}$ , which are tiled by the block sizes  $B_{Lkv}$  and  $B_{dqk}$  respectively.

Figure 3: TFLA Intra-Chunk Tiling. We loop over  $B_{Lkv}$  and  $B_{dqk}$  (indicated by arrows) and parallelize over  $B_{Lhq}$  and  $B_{dhv}$  (indicated by dashed lines) blocks.  $\bigoplus$  denotes block-wise accumulation.

**Tiled Computation.** For the mLSTM we cannot simply accumulate the results of the matrix multiplications  $\mathbf{H}_{\text{intra}}^{(k)}$  along the  $L_{kv}$  dimension and  $\mathbf{H}_{\text{inter}}^{(k)}$  due to the stabilization of the exponential input gate with the max state  $m_t$ . The max state tracks the maximum of the forget and input gates over time and is used to stabilize the exponential input gate similar to the safe softmax computation (Milakov & Gimelshein, 2018). Since we compute the hidden state output  $\mathbf{H}^{(k)}$  in blocks along the chunk size (i.e. time) dimension  $L_{kv}$ , we need to rescale during accumulation of the block results for  $\mathbf{H}_{\text{intra}}^{(k)}$  and the overall results into  $\mathbf{H}^{(k)}$  in the same way as FlashAttention (Dao, 2024). We provide details on the rescaling in Section B.2. For the backward pass there is no rescaling necessary as we store the max states in the forward pass and reuse them in the backward pass. The pseudocode for the forward pass of TFLA for the mLSTM is listed in Algorithm 1.

Backward Pass. The parallelization strategy for the backward pass of TFLA is more complex than for the forward pass, since we need to compute three output tensors — the gradients for the queries, keys and values, of which each has an intra-chunk and inter-chunk part. However, in Section C.4 we show that the individual gradients can be mapped to three matrix multiplications similar to the forward pass. In TFLA, we then implement a separate kernel for each gradient and use the same work partitioning as in the forward pass but swap the loop and parallelization dimensions, accordingly. Table 1 summarizes the work partitioning of our TFLA kernels.

Table 1: TFLA kernel parallelization and loop dimensions. Parallelization dimensions are indicated by P and loop dimensions by L. The last column shows the first two dimensions of the 3D kernel launch grid. The last dimension of all kernels is  $N_{\rm chunk} \cdot N_{\rm head} \cdot N_{\rm batch}$ .

| Kernel                      | $L_{hq}$ | $L_{kv}$ | $d_{qk}$ | $d_{hv}$ | Thread Block Grid                                                    |

|-----------------------------|----------|----------|----------|----------|----------------------------------------------------------------------|

| $\mathbf{H}^{(k)}$          | P        | L        | L        | P        | $\left(\frac{d_{hv}}{B_{dhv}}, \frac{L_{hq}}{B_{Lhq}}, \dots\right)$ |

| $\delta oldsymbol{Q}^{(k)}$ | P        | L        | P        | L        | $\left(\frac{d_{qk}}{B_{dqk}}, \frac{L_{hq}}{B_{Lhq}}, \dots\right)$ |

| $\delta oldsymbol{K}^{(k)}$ | L        | P        | P        | L        | $\left(\frac{d_{qk}}{B_{dqk}}, \frac{L_{kv}}{B_{Lkv}}, \dots\right)$ |

| $\delta oldsymbol{V}^{(k)}$ | L        | P        | L        | P        | $\left(\frac{d_{hv}}{B_{dhv}}, \frac{L_{kv}}{B_{Lkv}}, \dots\right)$ |

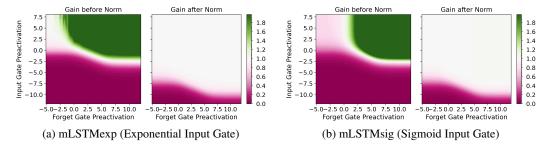

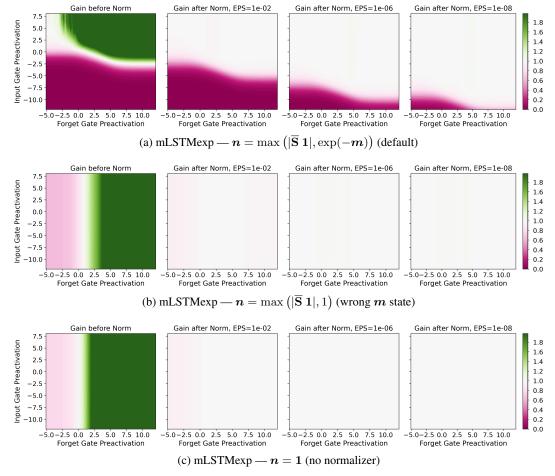

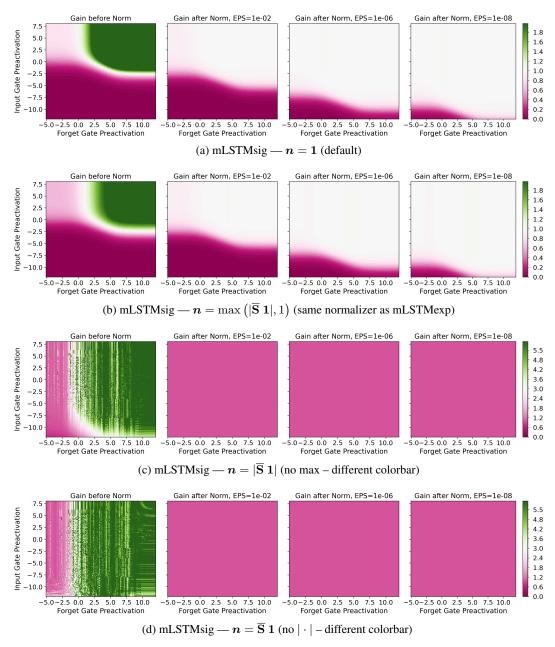

Figure 4: Transfer behavior of the mLSTM before and after the RMS-norm layer ( $\epsilon = 1e-6$ ) for different input and forget gate values. The color shows the gain of the mLSTM defined in (16). After the norm layer mLSTMexp and mLSTMsig exhibit the same transfer behavior.

# **Faster mLSTM with Sigmoid Input Gate**

The mLSTM with exponential gating (i.e. exponential input gate) introduced by Beck et al. (2024) requires to compute and keep track of two additional states, the normalizer state  $n_t$  and max state  $m_t$ , as we show in Appendix D.1. Both will increase kernel runtime: The normalizer must be computed through summations, and tracking the max state throughout the tiled computation in TFLA (see Section 3 and C.2) prevents efficient fusing of loops within the kernel (see Appendix C.3).

Additionally, our analysis in Section 4.2 suggests to initialize the input gate biases at larger negative values (e.g. -10), such that the input gate pre-activations can grow slowly during training. We observe that most of these values stay below 0 during training (see Figure 15 in Appendix E). Therefore, we seek an alternative activation function which is similar to the exponential function in the negative range, but bounded in the positive range. This suggests to use the sigmoid function  $\sigma(x) = \frac{1}{1 + \exp(-x)} = \frac{\exp(x)}{\exp(x) + 1}$ , which converges to  $\exp(x)$  for  $x \to -\infty$  and 1 for  $x \to \infty$ .

#### 4.1 mLSTM with Sigmoid Input Gate

The sigmoid function can be computed in two ways as given above. Depending on the sign of x it can be ensured that the argument of exp is always smaller than 0 to avoid numerical overflow. Therefore, we do not need to control the magnitude of x externally with a max state and as a consequence also drop the normalizer state (see Appendix D.1). This yields the mLSTM with sigmoid input gate (henceforth referred to as *mLSTMsig*) in its recurrent formulation as

$$\boldsymbol{C}_{t} = \sigma(\tilde{\mathbf{f}}_{t}) \, \boldsymbol{C}_{t-1} + \sigma(\tilde{\mathbf{i}}_{t}) \, \boldsymbol{k}_{t} \, \boldsymbol{v}_{t}^{\top}$$

(13)

$$\widetilde{\boldsymbol{h}}_t = \boldsymbol{C}_t^{\top} \left( \boldsymbol{q}_t / \sqrt{d_{qk}} \right) \tag{14}$$

$$\widetilde{\boldsymbol{h}}_{t} = \boldsymbol{C}_{t}^{\top} \left( \boldsymbol{q}_{t} / \sqrt{d_{qk}} \right)$$

$$\boldsymbol{h}_{t} = \sigma \left( \tilde{\boldsymbol{o}}_{t} \right) \odot \text{ NORM} \left( \widetilde{\boldsymbol{h}}_{t} \right)$$

(14)

where the query, key, and value vectors  $q_t, k_t, v_t$ , and the gate preactivations  $\tilde{i}_t, \tilde{f}_t, \tilde{o}_t$  remain the same as for the mLSTM with exponential input gate (from now on referred to as mLSTMexp) in Section 2.1. We confirm that our TFLA mLSTMsig forward kernel is over 30% faster than the mLSTMexp forward (see Section 5.2), and show that mLSTMsig performs equally well compared to mLSTMexp in our language modeling experiments up to 1.4B parameters (see Section 5.1).

#### 4.2 Normalization of mLSTM and Linear RNNs

Motivated by the performance of mLSTMsig, we seek to understand the differences between mL-STMsig and mLSTMexp empirically. To approach this, we draw inspiration from the concept of frequency response and transfer function analysis for control systems design, where typically the amplitude ratio or gain of output and input signals for different frequencies is considered (Ogata, 2010, Ch. 7). In our case, we analyze the transfer behavior of mLSTMsig and mLSTMexp for random inputs  $q_t, k_t$  and  $v_t$  and different input gate and forget gate preactivations  $i_t$  and  $f_t$ .

We will see that the normalization layer y = NORM(x), will play a crucial role in our analysis. The default norm layer in language modeling, the RMS norm (Zhang & Sennrich, 2019) with input vector input vector  $x \in \mathbb{R}^d$  and output vector  $y \in \mathbb{R}^d$  is defined as  $y = \frac{x}{\text{RMS}(x)} \odot \gamma$ , where

$\mathrm{RMS}(\boldsymbol{x}) = \sqrt{\frac{1}{d} \sum_{i=1}^d x_i^2 + \epsilon}$ , with with  $\boldsymbol{\gamma} \in \mathbb{R}^d$  being a learnable scale parameter. The epsilon parameter  $\epsilon \in \mathbb{R}$  is a small constant typically set to 1e-6 to avoid division by zero.

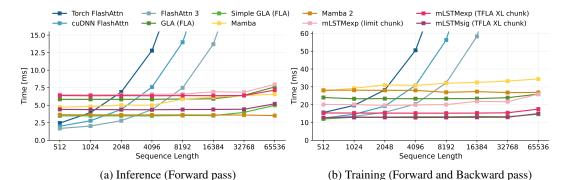

Figure 5: TFLA Kernel Runtime Benchmark for embedding dimension 4096 and 65,536 tokens on NVIDIA H100 GPUs. In training, our TFLA kernels are faster than FlashAttention 3 for longer sequences and over 2x faster than Mamba 2 kernels for all sequence lengths.

**Transfer Behavior of the mLSTM.** We analyze the transfer behavior by computing the gain of the mLSTM cells from random inputs sampled from  $\mathcal{N}(0,1)$  to hidden states before and after the norm layer for varying input and forget gate values. More specifically, we compute the gains  $G_{\text{before}}$  and  $G_{\text{after}}$  as

$$G_{\text{before}} = \frac{\|\widetilde{\boldsymbol{h}}_t\|_{\text{max}}}{\|\boldsymbol{v}_t\|_{\text{max}}} \quad \text{and} \quad G_{\text{after}} = \frac{\|\text{NORM}(\widetilde{\boldsymbol{h}}_t)\|_{\text{max}}}{\|\boldsymbol{v}_t\|_{\text{max}}},$$

(16)

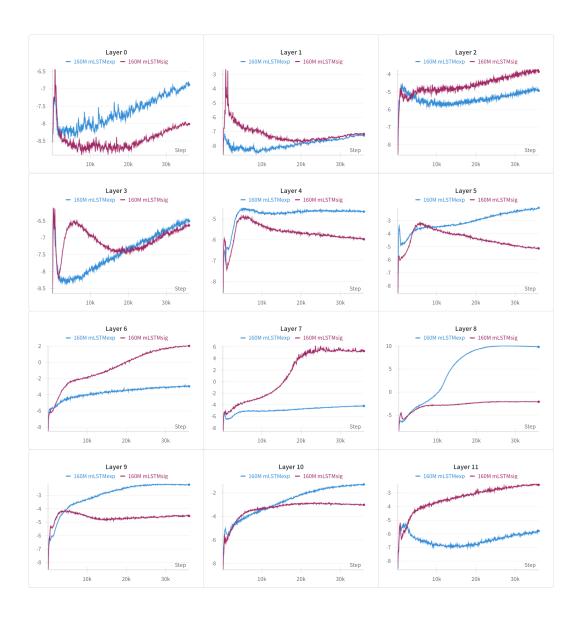

where  $\|\boldsymbol{x}\|_{\max} := \max(|\boldsymbol{x}_1|, \dots, |\boldsymbol{x}_d|)$  and we average over the time dimension. For more details see App. D.2. In Figure 4 we observe that the transfer behavior of mLSTMsig without normalizer is identical to mLSTMexp with normalizer and max state. Both exhibit a transition from suppressing (G=0) to passing (G=1) the signal at larger negative input gate preactivation values, which could partly explain the matching performance in our language modeling experiments.

Normalization Layers in other Gated Linear RNNs. Interestingly, almost all other gated linear RNN variants also place a normalization layer after the RNN cell (Sun et al., 2023; Dao & Gu, 2024; Qin et al., 2024b; Yang et al., 2024b). Often this is justified with improved training stability, but a more thorough discussion is missing (Lieber et al., 2024). Qin et al. (2022) analyze the effect of the norm layer after a non-gated, kernel-based linear attention layer (Katharopoulos et al., 2020) and show that this effectively prevents unbounded gradients. We also confirm that the norm layer has a significant impact on training stability and the gradient norm during training. In Section 5.1 we show that initializing the input gate bias at larger negative values, as suggested by our transfer behavior analysis in Figure 4, prevents large gradient norm variance and spikes during training. Relatedly, the general effect of layer normalization in the Transformer architecture has been investigated in several studies (Xiong et al., 2020; Zhu et al., 2025).

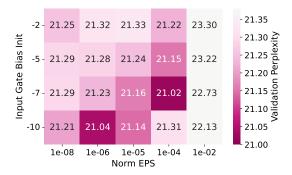

Effect of Normalization on Gating in Linear RNNs. We hypothesize that at this point the normalization layer does not only have a stabilizing effect by controlling the magnitude of the layer activations through rescaling, but also actively participates in the information routing or gating mechanism of the linear RNN. For example, if the squared norm of  $C_t^{\top}q$ , which is controlled by input and forget gates through  $C_t^{\top}$ , is smaller than the epsilon, the denominator in the NORM(x) layer is dominated by  $\epsilon$  and the output moves towards zero (indicated by the purple area in Fig. 4). Hence, by moving through the x-y plane in Fig. 4, the gates could learn to suppress or amplify any input in the sequence. In Section D.2 we show additional experiments on the effect of varying the normalization layer epsilons and different modifications of the normalizers for the mLSTM.

#### 5 Experiments

In this section, we examine the performance of the two mLSTM variants mLSTMexp (mLSTM with exponential input gate) and mLSTMsig (mLSTM with sigmoid input gate). We compare two kernel algorithms: (1) limit\_chunk: A kernel that is limited in chunk size L. (2) xl\_chunk: Our Tiled Flash Linear Attention (TFLA) kernels with unlimited chunk size. For details see Section 3. We assess the performance of mLSTMsig compared to mLSTMexp in Section 5.1 and benchmark the runtime of our kernels against other baselines in Section 5.2. In App. E.1 we verify the numerical correctness of our kernels.

#### 5.1 Language Modeling with mLSTM

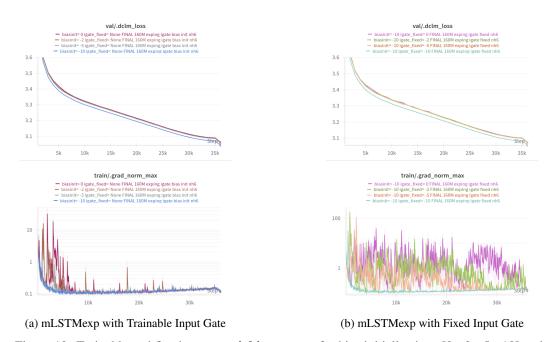

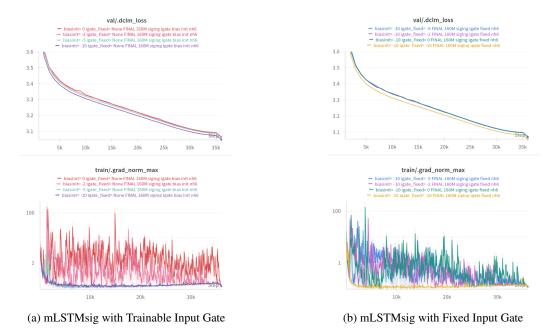

We train three different model sizes (160M, 400M, 1.4B parameters) with context lengths 4096 and 8192 on the DCLM dataset (Li et al., 2024). We include Llama2 style Transformer models (Touvron et al., 2023b) as reference in our comparison and describe our experiment setup, model architecture and training recipe in Appendix E.2.

Performance in Language Modeling. We compare mLSTMsig and mLSTMexp models on next-token prediction with different number of heads or head dimensions. Table 2 and Table 6 show the results for context length 4096 and 8192, respectively. We find that our limit\_chunk and xl\_chunk kernels yield the same loss (up to small numerical deviations) for almost all head dimensions. For some head dimensions, we observe gradient norm or loss spikes for the xl\_chunk kernels, which affect the final loss. As a main result we find that mLSTMsig performs equally well compared to mLSTMexp.

**Performance in Language Modeling.** We compare mLSTMsig and mLSTMexp models on next-token prediction with different number of heads or head dimensions. Table 2 and Table 2: Validation Perplexity at context length 4096. EXP and SIG denote mLSTMexp and mLSTMsig. LIMIT and XL correspond to 1imit\_chunk and xl\_chunk kernels.

| Size | Tokens | Heads        | Llama | EXP<br>LIMIT            | EXP<br>XL                | SIG<br>XL               |

|------|--------|--------------|-------|-------------------------|--------------------------|-------------------------|

| 160M | 19B    | 6<br>12      | 20.89 | 21.03<br>21.03          | 21.18<br>21.06           | 21.03<br>21.05          |

| 400M | 24B    | 4<br>8<br>16 | 16.85 | 16.66<br>16.55<br>16.60 | 16.66<br>16.80<br>16.61  | 16.67<br>16.67<br>16.61 |

| 1.4B | 33B    | 4<br>8<br>16 | 13.64 | 13.31<br>13.20<br>13.20 | 13.35<br>13.22<br>13.87* | 13.34<br>13.21<br>13.22 |

**Effect of Input Gate Bias Initialization.** We analyze the effect of the input gate bias initialization on training stability and performance of our mLSTM models in Appendix E.2. We observe in Figure 12 and 13, that initializing the input gate biases to -10 effectively mitigates large gradient norm spikes and variance during training for both mLSTMexp and mLSTMsig. We therefore conclude that the additional input gate not only improves performance (see Table 7), but also improves training stability, if initialized correctly.

**Effect of Norm Layer Epsilon.** In Appendix E.2, we investigate the effect of the norm layer epsilon on language modeling performance for mLSTMexp. Our transfer behavior analysis in Figure 4 suggests, that there exists an interplay between norm layer epsilon and input gate bias initialization. We confirm this in our grid search in Figure 14 and find that the best performing configuration is the default epsilon  $\epsilon = 1\text{e-}6$  with input gate biases initialized to -10.

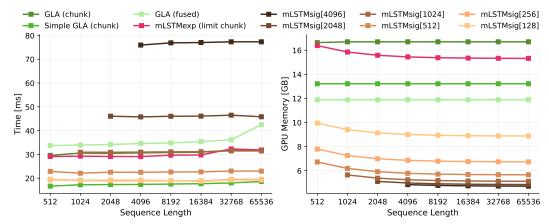

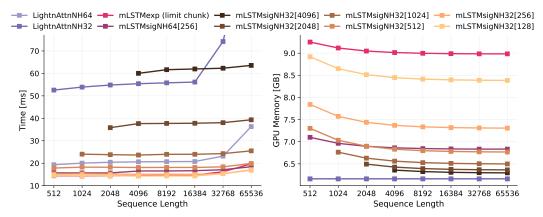

#### 5.2 Kernel Benchmark

We compare the runtime of our mLSTM limit\_chunk and TFLA xl\_chunk kernels with kernel implementations of the state-of-the-art sequence modeling primitives FlashAttention (Dao, 2024; Shah et al., 2024), Mamba (Gu & Dao, 2024; Dao & Gu, 2024) and GLA Yang et al. (2024b). In Appendix E.3 we compare with other kernels from the FlashLinearAttention library (Yang & Zhang, 2024). We run our benchmarks on NVIDIA H100 GPUs.

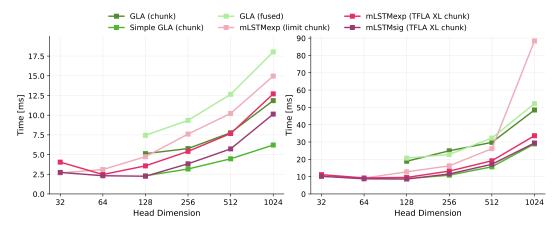

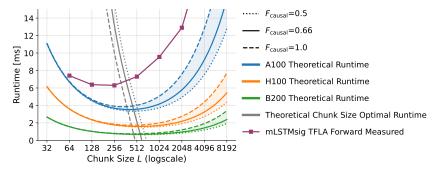

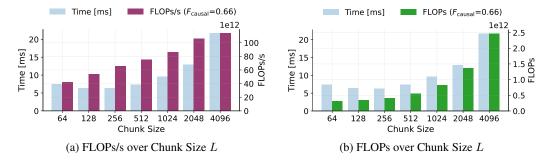

Runtime Benchmark. We use the standard embedding dimension of 4096 for 7B parameter models and adapt the head dimensions per kernel accordingly. For example for FlashAttention we use 32 heads with head dim 128 and for the mLSTM we use 16 heads with head dim 256. Following the practice of Shah et al. (2024), we keep the number of tokens constant at 65,536 and vary sequence length and batch size accordingly. For further details see Appendix E.3. Figure 5 shows the runtime benchmark results for inference, i.e. forward pass only, (left) and for training, i.e. forward-backward pass (right). Our mLSTMexp TFLA x1\_chunk kernels with two level sequence parallelism is about 25% faster than our limit\_chunk kernels. Through targeted modifications of the input gate of the mLSTM we save computation and enable more efficient kernel implementations for the forward pass of mLSTMsig (see Sec. 4). This yields another speedup of over 30% for the forward pass of the mLSTMsig TFLA kernel over the mLSTMexp TFLA kernel.

In training, our TFLA kernels are faster than FlashAttention 3 for longer sequences and more than 2x faster than Mamba 2 kernels for all sequence lengths. We perform additional runtime benchmarks for varying head dimensions and a more in-depth comparison to the FLA (Yang et al., 2024b) and LightningAttention2 (Qin et al., 2024a) kernels in Appendix E.3.

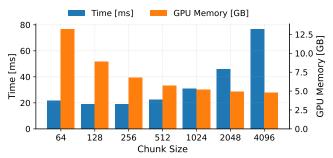

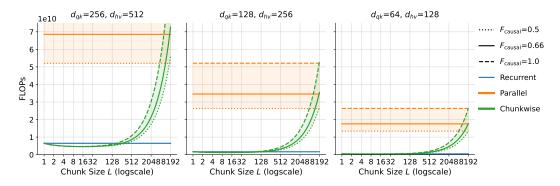

Runtime vs. Memory Trade-off. The chunk size parameter L balances the computation between the two levels of sequence parallelism (see Sec. 3). Smaller chunk sizes increase memory consumption, because more chunks are materialized in memory, but they reduce the quadratic compute FLOPs in the parallel part. Larger chunk sizes have the opposite effect. They decrease memory consumption, but increase quadratic compute FLOPs. In Figure 6, we measure this trade-off for our mLSTMsig TFLA x1\_chunk kernels.

Figure 6: Memory vs. Runtime Trade-off of TFLA Forward-Backward Pass. We show the mLSTMsig for embedding dimension 4096 (8 heads with dim 512), sequence length 8192 and batch size 8. By varying the chunk size parameter, TFLA kernels can effectively balance memory vs. runtime.

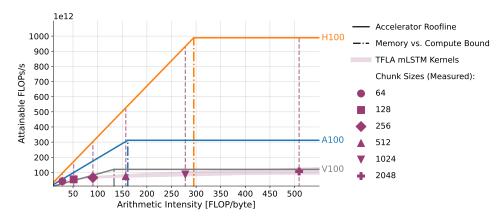

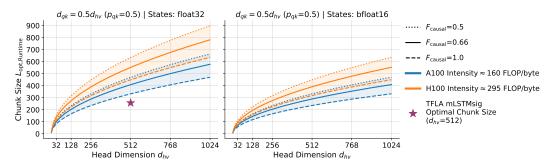

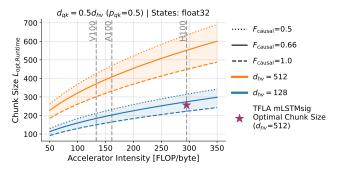

#### 5.3 Theoretical Runtime and Arithmetic Intensity

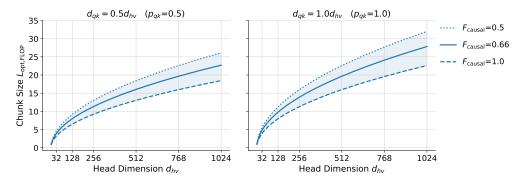

In Figure 6, we empirically observe that there exists an optimal chunk size (between 128 and 256) at which the runtime is minimized. In Appendix G, we compute the theoretical runtime optimal chunksize and the arithmetic intensity of TFLA depending on the chunk size by taking the FLOPs, memory operations and hardware accelerator specification into account. We find that the theoretical runtime optimum exceeds the empirically observed one (see Figure 21 in Appendix G.1), suggesting that our current kernel implementations may not yet fully exploit the available performance potential. We analyze the effect of the chunk size parameter L on runtime, FLOPs, and arithmetic intensity in detail in Appendix F and G summarize our findings as follows:

(1) The chunk size L mediates a trade-off between runtime and GPU memory usage [Figure 6]. (2) L determines the total compute in FLOPs: L=1 matches the recurrent formulation, while L=T matches the parallel one [Figure 19]. (3) There exists an optimal chunk size  $L \in [1,T]$  that minimized the total FLOP count [Equation (103), Figure 19, Figure 20]. (4) Increasing L raises the arithmetic intensity of TFLA kernels [Equation (109), Figure 22]. (5) The chunk size determines whether the kernel is memory-bound or compute-bound on a given hardware [Figure 23, Figure 22]. (6) FLOPs/s alone can be misleading; the optimal chunk size should be chosen based on total runtime [Figure 24, Figure 21]. (7) The runtime-optimal chunk size scales proportionally with the square root of the head dimension and the accelerator's computational intensity [Figure 25, Figure 26]. (8) Newer hardware generations require larger chunk sizes to approach peak performance. [Figure 26, Figure 21].

#### 6 Related Work

Tiled Flash Linear Attention (TFLA) integrates the concept of tiling along one sequence dimension of the attention matrix for improved work partitioning (Dao, 2024) with the strategy of dividing the sequence into chunks (Yang et al., 2024b), yielding two levels of sequence parallelism (see Figure 7).

**Flash Attention.** Flash Attention (Dao et al., 2022) is an IO-aware implementation of softmax attention introduced by (Vaswani et al., 2017). It uses the idea of tiling to reduce the number of memory reads/writes between GPU high bandwidth memory (HBM) and GPU on-chip SRAM. In this way the quadratic attention matrix  $QK^{\top}$  is never materialized in HBM, which reduces the memory requirement from quadratic with sequence length to linear, and significantly speeds up the kernel due to reduced memory IO cost. However, the computation still remains quadratic with sequence length. Flash Attention 2 (Dao, 2024) improves the work partitioning by parallelizing the attention computation over the sequence dimension in addition to the naive parallelization over batch and head dimension. Flash Attention 3 (Shah et al., 2024) leverages new hardware features of recent GPU generations (e.g. NVIDIA Hopper GPUs) such as FP8 precision or exploiting asynchrony of Tensor cores and Tensor Memory Accelerators (TMA) to speed up Flash Attention.

TFLA is IO-aware and parallelizes over one sequence dimension of the intra-chunk  $QK^{\top}$  matrix as the second level of sequence parallelism. New hardware features will also speed up future TFLA implementations.

Figure 7: Tiled Flash Linear Attention (TFLA) combines Flash Linear Attention and Flash Attention 2.

Flash Linear Attention. Flash Linear Attention (FLA) (Yang et al., 2024b; Yang & Zhang, 2024) makes use of the fact that linear attention can be interpreted as linear RNN (Katharopoulos et al., 2020). It then leverages the chunkwise-parallel formulation of linear RNNs (Hua et al., 2022; Sun et al., 2023) for efficient kernel implementations, that process the sequence in chunks. More specifically, Yang et al. (2024b) propose two FLA variants: A version that materializes intermediate states in HBM and a non-materialization version. The materialization version consists of two kernels: The first is a recurrent kernel that materializes the first intermediate states of every chunk. The second kernel then processes all chunks in parallel and computes the outputs within the chunks. The non-materialization version was proposed concurrently by Qin et al. (2024a) and does not employ parallelism over the sequence dimension, but processes the inputs sequentially in chunks.

TFLA uses the idea of chunking of the sequence for the first level of sequence parallelism.

**Application of TFLA to other Linear RNNs.** While TFLA is designed for efficient mLSTM kernels (Beck et al., 2024), its formulation also extends naturally to other linear RNNs such as RetNet, Mamba 2, and DeltaNet (Sun et al., 2023, 2024; Dao & Gu, 2024; Yang et al., 2024a). A more detailed discussion of these extensions is provided in Appendix A.

#### 7 Conclusion and Future Work

With Tiled Flash Linear Attention (TFLA) we introduce an algorithm for linear RNN and mLSTM kernels with two levels of sequence parallelism. Our TFLA kernels for the mLSTM with exponential input gate (mLSTMexp) achieve state-of-the art kernel execution speeds, while remaining flexible to trade off GPU memory consumption and runtime. To further improve kernel runtimes, we propose mLSTMsig, a mLSTM variant with sigmoid input gate, that reduces computation and increases speed. Our experiments show that both mLSTM variants perform equally well on language modeling.

Although we enhance training stability through careful gate initialization informed by our empirical transfer behavior analysis, future work could explore instabilities arising from numerical errors in kernel implementations in greater depth. Finally, the programming techniques and hardware features used to optimize FlashAttention (Shah et al., 2024) could also be applied to our TFLA algorithm to approach peak performance on next-generation hardware, as suggested by our theoretical runtime analysis. This makes us believe that TFLA has the potential to become a foundational primitive for future long-context language models.

# Acknowledgements

We thank Sebastian Böck, Richard Kurle, Patrick Blies, Antonio Orvieto, Maximilian Stadler, Thomas Schmied, Kajetan Schweighofer and Sebastian Lehner for helpful discussions and feedback.

#### References

Alharthi, M. and Mahmood, A. xLSTMTime: Long-term time series forecasting with xLSTM. *AI*, 5 (3):1482–1495, 2024. ISSN 2673-2688. doi: 10.3390/ai5030071. URL https://www.mdpi.com/2673-2688/5/3/71.

- Alkin, B., Beck, M., Pöppel, K., Hochreiter, S., and Brandstetter, J. Vision-LSTM: xLSTM as generic vision backbone. In *International Conference on Learning Representations*, 2025. URL https://openreview.net/forum?id=SiH7DwNKZZ.

- Austin, J., Douglas, S., Frostig, R., Levskaya, A., Chen, C., Vikram, S., Lebron, F., Choy, P., Ramasesh, V., Webson, A., and Pope, R. How to scale your model. 2025. Retrieved from https://jax-ml.github.io/scaling-book/.

- Ba, J. L., Kiros, J. R., and Hinton, G. E. Layer Normalization. *arXiv*, 1607.06450, 2016. URL https://arxiv.org/abs/1607.06450.

- Beck, M., Pöppel, K., Spanring, M., Auer, A., Prudnikova, O., Kopp, M., Klambauer, G., Brandstetter, J., and Hochreiter, S. xLSTM: Extended long short-term memory. In *Thirty-eighth Conference on Neural Information Processing Systems*, 2024. URL https://arxiv.org/abs/2405.04517.

- Beck, M., Pöppel, K., Lippe, P., Kurle, R., Blies, P. M., Klambauer, G., Böck, S., and Hochreiter, S. xLSTM 7b: A recurrent LLM for fast and efficient inference. In *Forty-second International Conference on Machine Learning*, 2025. URL https://openreview.net/forum?id=LV3DpKD08B.

- Black, S., Biderman, S., Hallahan, E., Anthony, Q., Gao, L., Golding, L., He, H., Leahy, C., McDonell, K., Phang, J., Pieler, M., Prashanth, U. S., Purohit, S., Reynolds, L., Tow, J., Wang, B., and Weinbach, S. GPT-NeoX-20B: An open-source autoregressive language model. In *Proceedings of the ACL Workshop on Challenges & Perspectives in Creating Large Language Models*, 2022. URL https://arxiv.org/abs/2204.06745.

- Bradbury, J., Frostig, R., Hawkins, P., Johnson, M. J., Leary, C., Maclaurin, D., Necula, G., Paszke, A., VanderPlas, J., Wanderman-Milne, S., and Zhang, Q. JAX: composable transformations of Python+NumPy programs, 2018. URL http://github.com/jax-ml/jax.

- Brown, T., Mann, B., Ryder, N., Subbiah, M., Kaplan, J. D., Dhariwal, P., Neelakantan, A., Shyam, P., Sastry, G., Askell, A., et al. Language models are Few-Shot Learners. *Advances in neural information processing systems*, 33:1877–1901, 2020.

- Dao, T. FlashAttention-2: Faster Attention with Better Parallelism and Work Partitioning. In *The Twelfth International Conference on Learning Representations*, 2024. URL https://openreview.net/forum?id=mZn2Xyh9Ec.

- Dao, T. and Gu, A. Transformers are SSMs: Generalized models and efficient algorithms through structured state space duality. In *Forty-first International Conference on Machine Learning*, 2024. URL https://openreview.net/forum?id=ztn8FCR1td.

- Dao, T., Fu, D. Y., Ermon, S., Rudra, A., and Ré, C. FlashAttention: Fast and memory-efficient exact attention with IO-awareness. In *Advances in Neural Information Processing Systems (NeurIPS)*, 2022.

- Fu, D. Y., Kumbong, H., Nguyen, E., and Ré, C. FlashFFTConv: Efficient convolutions for long sequences with tensor cores. In *International Conference on Learning Representations*, 2024.

- Gholami, A., Yao, Z., Kim, S., Hooper, C., Mahoney, M. W., and Keutzer, K. AI and Memory Wall. *IEEE Micro*, 44(03):33–39, May 2024. ISSN 1937-4143. doi: 10.1109/MM.2024.3373763. URL https://doi.ieeecomputersociety.org/10.1109/MM.2024.3373763.

- Grazzi, R., Siems, J., Franke, J. K., Zela, A., Hutter, F., and Pontil, M. Unlocking state-tracking in linear RNNs through negative eigenvalues. In *International Conference on Learning Representations*, 2025. URL https://openreview.net/forum?id=UvTo3tVBk2.

- Gu, A. and Dao, T. Mamba: Linear-time sequence modeling with selective state spaces. In International Conference on Learning Representations, 2024. URL https://openreview.net/ forum?id=AL1fq05o7H.

- Heek, J., Levskaya, A., Oliver, A., Ritter, M., Rondepierre, B., Steiner, A., and van Zee, M. Flax: A neural network library and ecosystem for JAX, 2024. URL http://github.com/google/flax.

- Hochreiter, S. Untersuchungen zu dynamischen neuronalen Netzen. Master's thesis, Technische Universität München, 1991.

- Hochreiter, S. and Schmidhuber, J. Long short-term memory. Neural Computation, 9(8):1735–1780, 1997.

- Hua, W., Dai, Z., Liu, H., and Le, Q. Transformer quality in linear time. In Chaudhuri, K., Jegelka, S., Song, L., Szepesvari, C., Niu, G., and Sabato, S. (eds.), Proceedings of the 39th International Conference on Machine Learning, volume 162 of Proceedings of Machine Learning Research, pp. 9099–9117. PMLR, 17–23 Jul 2022. URL https://proceedings.mlr.press/v162/hua22a.html.

- Jia, X., Donat, A., Huang, X., Zhao, X., Blessing, D., Zhou, H., Wang, H. A., Zhang, H., Wang, Q., Lioutikov, R., and Neumann, G. X-IL: Exploring the design space of imitation learning policies. *arXiv*, 2502.12330, 2025. URL https://arxiv.org/abs/2502.12330.

- Katharopoulos, A., Vyas, A., Pappas, N., and Fleuret, F. Transformers are RNNs: Fast autoregressive transformers with linear attention. In *Proceedings of the International Conference on Machine Learning*, 2020.

- Katsch, T. GateLoop: Fully data-controlled linear recurrence for sequence modeling. *ArXiv*, 2311.01927, 2023.

- Kong, Y., Wang, Z., Nie, Y., Zhou, T., Zohren, S., Liang, Y., Sun, P., and Wen, Q. Unlocking the power of lstm for long term time series forecasting. *arXiv*, 2408.10006, 2025. URL https://arxiv.org/abs/2408.10006.

- Kraus, M., Divo, F., Dhami, D. S., and Kersting, K. xlstm-mixer: Multivariate time series forecasting by mixing via scalar memories. *arXiv*, 2410.16928, 2024. URL https://arxiv.org/abs/2410.16928.

- Li, J., Fang, A., Smyrnis, G., Ivgi, M., Jordan, M., Gadre, S., Bansal, H., Guha, E., Keh, S., Arora, K., Garg, S., Xin, R., Muennighoff, N., Heckel, R., Mercat, J., Chen, M., Gururangan, S., Wortsman, M., Albalak, A., Bitton, Y., Nezhurina, M., Abbas, A., Hsieh, C.-Y., Ghosh, D., Gardner, J., Kilian, M., Zhang, H., Shao, R., Pratt, S., Sanyal, S., Ilharco, G., Daras, G., Marathe, K., Gokaslan, A., Zhang, J., Chandu, K., Nguyen, T., Vasiljevic, I., Kakade, S., Song, S., Sanghavi, S., Faghri, F., Oh, S., Zettlemoyer, L., Lo, K., El-Nouby, A., Pouransari, H., Toshev, A., Wang, S., Groeneveld, D., Soldaini, L., Koh, P. W., Jitsev, J., Kollar, T., Dimakis, A. G., Carmon, Y., Dave, A., Schmidt, L., and Shankar, V. Datacomp-lm: In search of the next generation of training sets for language models. *arXiv*, 2406.11794, 2024. URL https://arxiv.org/abs/2406.11794.

- Lieber, O., Lenz, B., Bata, H., Cohen, G., Osin, J., Dalmedigos, I., Safahi, E., Meirom, S., Belinkov, Y., Shalev-Shwartz, S., Abend, O., Alon, R., Asida, T., Bergman, A., Glozman, R., Gokhman, M., Manevich, A., Ratner, N., Rozen, N., Shwartz, E., Zusman, M., and Shoham, Y. Jamba: A hybrid transformer-mamba language model. *arXiv*, 2403.19887, 2024. URL https://arxiv.org/abs/2403.19887.

- Loshchilov, I. and Hutter, F. Decoupled weight decay regularization. In *International Conference on Learning Representations*, 2019. URL https://openreview.net/forum?id=Bkg6RiCqY7.

- Milakov, M. and Gimelshein, N. Online normalizer calculation for softmax. *ArXiv*, 1805.02867, 2018.

- MiniMax, Li, A., Gong, B., Yang, B., Shan, B., Liu, C., Zhu, C., Zhang, C., Guo, C., Chen, D., Li, D., Jiao, E., Li, G., Zhang, G., Sun, H., Dong, H., Zhu, J., Zhuang, J., Song, J., Zhu, J., Han, J., Li, J., Xie, J., Xu, J., Yan, J., Zhang, K., Xiao, K., Kang, K., Han, L., Wang, L., Yu, L., Feng, L., Zheng, L., Chai, L., Xing, L., Ju, M., Chi, M., Zhang, M., Huang, P., Niu, P., Li, P., Zhao, P., Yang, Q., Xu, Q., Wang, Q., Wang, Q., Li, Q., Leng, R., Shi, S., Yu, S., Li, S., Zhu, S., Huang, T., Liang, T., Sun, W., Sun, W., Cheng, W., Li, W., Song, X., Su, X., Han, X., Zhang, X., Hou, X., Min, X., Zou, X., Shen, X., Gong, Y., Zhu, Y., Zhou, Y., Zhong, Y., Hu, Y., Fan, Y., Yu, Y., Yang, Y., Li, Y., Huang, Y., Li, Y., Huang, Y., Xu, Y., Mao, Y., Li, Z., Li, Z., Tao, Z., Ying, Z., Cong, Z., Qin, Z., Fan, Z., Yu, Z., Jiang, Z., and Wu, Z. MiniMax-01: Scaling foundation models with lightning attention. arXiv, 2501.08313, 2025. URL https://arxiv.org/abs/2501.08313.

- Movahedi, S., Sarnthein, F., Cirone, N. M., and Orvieto, A. Fixed-point rnns: From diagonal to dense in a few iterations. *arXiv*, 2503.10799, 2025. URL https://arxiv.org/abs/2503.10799.

- Ogata, K. *Modern control engineering*. Prentice-Hall electrical engineering series. Instrumentation and controls series. Prentice-Hall, Boston, 5th ed edition, 2010. ISBN 978-0-13-615673-4.

- Orvieto, A., Smith, S. L., Gu, A., Fernando, A., Gulcehre, C., Pascanu, R., and De, S. Resurrecting recurrent neural networks for long sequences. *arXiv*, 2303.06349, 2023. URL https://arxiv.org/abs/2303.06349.

- Paszke, A., Gross, S., Massa, F., Lerer, A., Bradbury, J., Chanan, G., Killeen, T., Lin, Z., Gimelshein, N., Antiga, L., Desmaison, A., Köpf, A., Yang, E., DeVito, Z., Raison, M., Tejani, A., Chilamkurthy, S., Steiner, B., Fang, L., Bai, J., and Chintala, S. Pytorch: An imperative style, high-performance deep learning library. arXiv, 1912.01703, 2019. URL https://arxiv.org/abs/1912.01703.

- Peng, B., Goldstein, D., Anthony, Q., Albalak, A., Alcaide, E., Biderman, S., Cheah, E., Du, X., Ferdinan, T., Hou, H., Kazienko, P., GV, K. K., Kocoń, J., Koptyra, B., Krishna, S., Jr., R. M., Lin, J., Muennighoff, N., Obeid, F., Saito, A., Song, G., Tu, H., Wirawan, C., Woźniak, S., Zhang, R., Zhao, B., Zhao, Q., Zhou, P., Zhu, J., and Zhu, R.-J. Eagle and finch: Rwkv with matrix-valued states and dynamic recurrence. *arXiv*, 2404.05892, 2024. URL https://arxiv.org/abs/2404.05892.

- Peng, B., Zhang, R., Goldstein, D., Alcaide, E., Hou, H., Lu, J., Merrill, W., Song, G., Tan, K., Utpala, S., Wilce, N., Wind, J. S., Wu, T., Wuttke, D., and Zhou-Zheng, C. Rwkv-7 "goose" with expressive dynamic state evolution. *arXiv*, 2503.14456, 2025. URL https://arxiv.org/abs/2503.14456.

- Pöppel, K., Beck, M., and Hochreiter, S. FlashRNN: I/O-aware optimization of traditional RNNs on modern hardware. In *The Thirteenth International Conference on Learning Representations*, 2025. URL https://openreview.net/forum?id=10ZzTvPfTw.

- Qin, Z., Han, X., Sun, W., Li, D., Kong, L., Barnes, N., and Zhong, Y. The devil in linear transformer. In Goldberg, Y., Kozareva, Z., and Zhang, Y. (eds.), *Proceedings of the 2022 Conference on Empirical Methods in Natural Language Processing*, pp. 7025–7041, Abu Dhabi, United Arab Emirates, December 2022. Association for Computational Linguistics. doi: 10.18653/v1/2022. emnlp-main.473. URL https://aclanthology.org/2022.emnlp-main.473/.

- Qin, Z., Sun, W., Li, D., Shen, X., Sun, W., and Zhong, Y. Lightning attention-2: A free lunch for handling unlimited sequence lengths in large language models. *arXiv*, 2401.04658, 2024a. URL https://arxiv.org/abs/2401.04658.

- Qin, Z., Yang, S., Sun, W., Shen, X., Li, D., Sun, W., and Zhong, Y. HGRN2: Gated linear RNNs with state expansion. In *First Conference on Language Modeling*, 2024b. URL https://openreview.net/forum?id=y6SqbJfCSk.

- Radford, A., Wu, J., Child, R., Luan, D., Amodei, D., and Sutskever, I. Language models are unsupervised multitask learners. *OpenAI*, 2019. URL https://cdn.openai.com/better-language-models/language\_models\_are\_unsupervised\_multitask\_learners.pdf.

- Schlag, I., Irie, K., and Schmidhuber, J. Linear transformers are secretly fast weight programmers. In *International Conference on Machine Learning*, 2021. URL https://proceedings.mlr.press/v139/schlag21a.html.

- Schmidinger, N., Schneckenreiter, L., Seidl, P., Schimunek, J., Hoedt, P.-J., Brandstetter, J., Mayr, A., Luukkonen, S., Hochreiter, S., and Klambauer, G. Bio-xLSTM: Generative modeling, representation and in-context learning of biological and chemical sequences. In *International Conference on Learning Representations*, 2025. URL https://openreview.net/forum?id=IjbXZdugdj.

- Schmied, T., Adler, T., Patil, V., Beck, M., Pöppel, K., Brandstetter, J., Klambauer, G., Pascanu, R., and Hochreiter, S. A large recurrent action model: xLSTM enables fast inference for robotics tasks. *arXiv*, 2410.22391, 2025. URL https://arxiv.org/abs/2410.22391.

- Shah, J., Bikshandi, G., Zhang, Y., Thakkar, V., Ramani, P., and Dao, T. Flashattention-3: Fast and accurate attention with asynchrony and low-precision. 2024. URL https://arxiv.org/abs/2407.08608.

- Shazeer, N. GLU variants improve transformer. *arXiv*, 2002.05202, 2020. URL https://arxiv.org/abs/2002.05202.

- Siems, J., Carstensen, T., Zela, A., Hutter, F., Pontil, M., and Grazzi, R. Deltaproduct: Increasing the expressivity of deltanet through products of householders. In *ICLR 2025 Workshop on Foundation Models in the Wild*, 2025. URL https://openreview.net/forum?id=nvb60szj5C.

- Spector, B. F., Arora, S., Singhal, A., Fu, D. Y., and Ré, C. ThunderKittens: Simple, fast, and adorable ai kernels. *arXiv*, 2410.20399, 2024. URL https://arxiv.org/abs/2410.20399.

- Sun, Y., Dong, L., Huang, S., Ma, S., Xia, Y., Xue, J., Wang, J., and Wei, F. Retentive network: A successor to transformer for large language models. *ArXiv*, 2307.08621, 2023.

- Sun, Y., Dong, L., Zhu, Y., Huang, S., Wang, W., Ma, S., Zhang, Q., Wang, J., and Wei, F. You Only Cache Once: Decoder-decoder architectures for language models. In *The Thirty-eighth Annual Conference on Neural Information Processing Systems*, 2024. URL https://openreview.net/forum?id=25Ioxw576r.

- Team, G. Gemma 2: Improving open language models at a practical size. *arXiv*, 2408.00118, 2024. URL https://arxiv.org/abs/2408.00118.

- Tillet, P. Triton, 2024. URL https://github.com/triton-lang/triton.

- Tillet, P., Kung, H. T., and Cox, D. Triton: an intermediate language and compiler for tiled neural network computations. In *Proceedings of the 3rd ACM SIGPLAN International Workshop on Machine Learning and Programming Languages*, MAPL 2019, pp. 10–19, New York, NY, USA, 2019. Association for Computing Machinery. ISBN 9781450367196. doi: 10.1145/3315508. 3329973. URL https://doi.org/10.1145/3315508.3329973.

- Touvron, H., Lavril, T., Izacard, G., Martinet, X., Lachaux, M.-A., Lacroix, T., Rozière, B., Goyal, N., Hambro, E., Azhar, F., Rodriguez, A., Joulin, A., Grave, E., and Lample, G. Llama: Open and efficient foundation language models. *arXiv*, 2302.13971, 2023a. URL https://arxiv.org/abs/2302.13971.

- Touvron, H., Martin, L., Stone, K., Albert, P., Almahairi, A., Babaei, Y., Bashlykov, N., Batra, S., Bhargava, P., Bhosale, S., Bikel, D., Blecher, L., Ferrer, C. C., Chen, M., Cucurull, G., Esiobu, D., Fernandes, J., Fu, J., Fu, W., Fuller, B., Gao, C., Goswami, V., Goyal, N., Hartshorn, A., Hosseini, S., Hou, R., Inan, H., Kardas, M., Kerkez, V., Khabsa, M., Kloumann, I., Korenev, A., Koura, P. S., Lachaux, M.-A., Lavril, T., Lee, J., Liskovich, D., Lu, Y., Mao, Y., Martinet, X., Mihaylov, T., Mishra, P., Molybog, I., Nie, Y., Poulton, A., Reizenstein, J., Rungta, R., Saladi, K., Schelten, A., Silva, R., Smith, E. M., Subramanian, R., Tan, X. E., Tang, B., Taylor, R., Williams, A., Kuan, J. X., Xu, P., Yan, Z., Zarov, I., Zhang, Y., Fan, A., Kambadur, M., Narang, S., Rodriguez, A., Stojnic, R., Edunov, S., and Scialom, T. Llama 2: Open foundation and fine-tuned chat models. *arXiv*, 2307.09288, 2023b. URL https://arxiv.org/abs/2307.09288.

- Vaswani, A., Shazeer, N., Parmar, N., Uszkoreit, J., Jones, L., Gomez, A. N., Kaiser, L. u., and Polosukhin, I. Attention is all you need. In Guyon, I., Luxburg, U. V., Bengio, S., Wallach, H., Fergus, R., Vishwanathan, S., and Garnett, R. (eds.), *Advances in Neural Information Processing Systems*, volume 30, 2017. URL https://arxiv.org/abs/1706.03762.

- Vikram, S., Jones, C., and Lebedev, S. Jax-triton, 2022. URL https://github.com/jax-ml/jax-triton.

- Waleffe, R., Byeon, W., Riach, D., Norick, B., Korthikanti, V., Dao, T., Gu, A., Hatamizadeh, A., Singh, S., Narayanan, D., Kulshreshtha, G., Singh, V., Casper, J., Kautz, J., Shoeybi, M., and Catanzaro, B. An empirical study of mamba-based language models. *arXiv*, 2406.07887, 2024. URL https://arxiv.org/abs/2406.07887.

- Williams, S., Waterman, A., and Patterson, D. Roofline: an insightful visual performance model for multicore architectures. *Commun. ACM*, 52(4):65–76, April 2009. ISSN 0001-0782. doi: 10.1145/1498765.1498785. URL https://doi.org/10.1145/1498765.1498785.

- Xiong, R., Yang, Y., He, D., Zheng, K., Zheng, S., Xing, C., Zhang, H., Lan, Y., Wang, L., and Liu, T. On layer normalization in the transformer architecture. In III, H. D. and Singh, A. (eds.), *Proceedings of the 37th International Conference on Machine Learning*, volume 119 of *Proceedings of Machine Learning Research*, pp. 10524–10533. PMLR, 13–18 Jul 2020. URL https://proceedings.mlr.press/v119/xiong20b.html.

- Yang, S. and Zhang, Y. FLA: A Triton-based library for hardware-efficient implementations of linear attention mechanism. January 2024. URL https://github.com/sustcsonglin/flash-linear-attention.

- Yang, S., Kautz, J., and Hatamizadeh, A. Gated delta networks: Improving mamba2 with delta rule. *arXiv*, 2412.06464, 2024a. URL https://arxiv.org/abs/2412.06464.

- Yang, S., Wang, B., Shen, Y., Panda, R., and Kim, Y. Gated linear attention transformers with hardware-efficient training. In *Forty-first International Conference on Machine Learning*, 2024b. URL https://openreview.net/forum?id=ia5XvxFUJT.

- Yang, S., Wang, B., Zhang, Y., Shen, Y., and Kim, Y. Parallelizing linear transformers with the delta rule over sequence length. In *The Thirty-eighth Annual Conference on Neural Information Processing Systems*, 2024c. URL https://openreview.net/forum?id=y8Rm4VNRPH.

- Zhang, B. and Sennrich, R. Root mean square layer normalization. In Wallach, H., Larochelle, H., Beygelzimer, A., d'Alché-Buc, F., Fox, E., and Garnett, R. (eds.), *Advances in Neural Information Processing Systems*, volume 32. Curran Associates, Inc., 2019. URL https://arxiv.org/abs/1910.07467.

- Zhu, J., Chen, X., He, K., LeCun, Y., and Liu, Z. Transformers without normalization. In *Proceedings* of the Computer Vision and Pattern Recognition Conference, pp. 14901–14911, 2025.

# **NeurIPS Paper Checklist**

#### 1. Claims

Question: Do the main claims made in the abstract and introduction accurately reflect the paper's contributions and scope?

Answer: [Yes]

Justification: We provide extensive experiments in the main paper and the appendix.

#### 2. Limitations

Question: Does the paper discuss the limitations of the work performed by the authors?

Answer: [Yes]

Justification: We point out efficiency limitations of our Triton kernel implementations on recent hardware generations in the theoretical runtime analysis and also report runs with numerical problems.

#### 3. Theory assumptions and proofs

Question: For each theoretical result, does the paper provide the full set of assumptions and a complete (and correct) proof?

Answer: [NA]

Justification: There are no Theorems or such in the paper.

# 4. Experimental result reproducibility

Question: Does the paper fully disclose all the information needed to reproduce the main experimental results of the paper to the extent that it affects the main claims and/or conclusions of the paper (regardless of whether the code and data are provided or not)?

Answer: [Yes]

Justification: We provide a thorough description of our experimental setup as well as Pseudocode for our algorithm in the Appendix. We will also release the software library for our kernel implementations.

# 5. Open access to data and code

Question: Does the paper provide open access to the data and code, with sufficient instructions to faithfully reproduce the main experimental results, as described in supplemental material?

Answer: [Yes]

Justification: Our code will be made publicly available.

#### 6. Experimental setting/details

Question: Does the paper specify all the training and test details (e.g., data splits, hyper-parameters, how they were chosen, type of optimizer, etc.) necessary to understand the results?

Answer: [Yes]

Justification: All details are provided in the Appendix, as well as the accompanying code.

### 7. Experiment statistical significance

Question: Does the paper report error bars suitably and correctly defined or other appropriate information about the statistical significance of the experiments?

Answer: [No]

Justification: Our language modeling experiments were too expensive to run multiple seeds.

#### 8. Experiments compute resources

Question: For each experiment, does the paper provide sufficient information on the computer resources (type of compute workers, memory, time of execution) needed to reproduce the experiments?

Answer: [Yes]

Justification: We state that our experiments were conducted on NVIDIA H100 GPUs.

#### 9. Code of ethics

Question: Does the research conducted in the paper conform, in every respect, with the NeurIPS Code of Ethics https://neurips.cc/public/EthicsGuidelines?

Answer: [Yes]

Justification: We conform with the code of ethics.

### 10. Broader impacts

Question: Does the paper discuss both potential positive societal impacts and negative societal impacts of the work performed?

Answer: [Yes]

Justification: We provide an impact statement in the appendix, just before the references.

#### 11. Safeguards

Question: Does the paper describe safeguards that have been put in place for responsible release of data or models that have a high risk for misuse (e.g., pretrained language models, image generators, or scraped datasets)?

Answer: [NA]

Justification: The paper does not pose such risks.

#### 12. Licenses for existing assets

Question: Are the creators or original owners of assets (e.g., code, data, models), used in the paper, properly credited and are the license and terms of use explicitly mentioned and properly respected?

Answer: [Yes]

Justification: All software licenses are respected.

#### 13. New assets

Question: Are new assets introduced in the paper well documented and is the documentation provided alongside the assets?

Answer: [Yes]

Justification: The code that will be released with the paper contains proper documentation.

# 14. Crowdsourcing and research with human subjects

Question: For crowdsourcing experiments and research with human subjects, does the paper include the full text of instructions given to participants and screenshots, if applicable, as well as details about compensation (if any)?

Answer: [NA]

Justification: The paper does not involve crowdsourcing or research with human subjects

# 15. Institutional review board (IRB) approvals or equivalent for research with human subjects

Question: Does the paper describe potential risks incurred by study participants, whether such risks were disclosed to the subjects, and whether Institutional Review Board (IRB) approvals (or an equivalent approval/review based on the requirements of your country or institution) were obtained?

Answer: [NA]

Justification: The paper does not involve crowdsourcing nor research with human subjects.

#### 16. Declaration of LLM usage

Question: Does the paper describe the usage of LLMs if it is an important, original, or non-standard component of the core methods in this research? Note that if the LLM is used only for writing, editing, or formatting purposes and does not impact the core methodology, scientific rigorousness, or originality of the research, declaration is not required.

Answer: [NA]

Justification: The core method development in this research does not involve LLMs as any important, original, or non-standard components.

# Appendix

# TABLE OF CONTENTS

| Appendix A - Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| A.1. Other Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19                               |

| A.2. Application of TFLA to other Linear RNNs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19                               |

| Appendix B - Extended mLSTM Formulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20                               |

| B.1. Fully Parallel Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |

| B.2. Detailed Chunkwise-Parallel Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21                               |

| B.3. Chunkwise-Parallel Backward Pass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  |

| Appendix C - Extended Tiled Flash Linear Attention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27                               |

| C.1. GPU Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  |

| C.2. Tiled Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                  |

| C.3. TFLA Forward Pass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                  |

| C.4. TFLA Backward Pass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30                               |

| Appendix D - Extended mLSTM with Sigmoid Input Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31                               |

| D.1. Stabilization of the Exponential Input Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| D.2. Empirical Transfer Behavior Analysis of the mLSTM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32                               |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |