# QUARCH: A BENCHMARK FOR EVALUATING LLM REASONING IN COMPUTER ARCHITECTURE

Anonymous authors

Paper under double-blind review

#### **ABSTRACT**

The field of computer architecture, which bridges high-level software abstractions and low-level hardware implementations, remains absent from current large language model (LLM) evaluations. To this end, we present QUARCH (pronounced 'quark'), the first benchmark designed to facilitate the development and evaluation of LLM knowledge and reasoning capabilities specifically in computer architecture. QUARCH provides a comprehensive collection of 2,671 expert-validated question-answer (QA) pairs covering various aspects of computer architecture, including processor design, memory systems, and interconnection networks. Our evaluation reveals that while frontier models possess domain-specific knowledge, they struggle with skills that require higher-order thinking in computer architecture. Frontier model accuracies vary widely (from 34% to 72%) on these advanced questions, highlighting persistent gaps in architectural reasoning across analysis, design, and implementation QAs. By holistically assessing fundamental skills, QUARCH provides a foundation for building and measuring LLM capabilities that can accelerate innovation in computing systems.

## 1 Introduction

Benchmarks that elicit reasoning are among the most impactful large language model (LLM) evaluations today since they require critical thinking that goes beyond surface-level knowledge and pattern matching. As a result, state-of-the-art (SoTA) progress is tracked on benchmark suites requiring multi-step reasoning, where models with explicit test-time deliberation (i.e., "thinking" variants) consistently climb leaderboards. Widely adopted datasets such as GSM8K (Cobbe et al., 2021), AIME (Mislav Balunović, 2025), SWE-bench (Jimenez et al., 2024), GPQA (Rein et al., 2023), and MMLU-Pro (Wang et al., 2024a) probe this structured reasoning to serve as proxies for measuring math, software engineering, and natural and physical science expertise.

Reasoning is equally central to *computer architecture*, which emphasizes evaluating trade-offs within a multi-objective optimization design space. For example, computer architects decide how to organize and balance components of systems (e.g., compute, memory, interconnects) and their power, performance, and area trade-offs. However, computer architecture remains an area without any LLM benchmarks to date.

Existing benchmarks in computing systems target engineering tasks for software or chip implementation such as code generation (Jimenez et al., 2023; Yang et al., 2024; OpenAI, 2024; He et al., 2025), register-transfer level (RTL) generation (Liu et al., 2023b; Pinckney et al., 2025b), system-on-chip (SoC) integration (Alvanaki et al., 2025), and chip verification (Wan et al., 2025). While these are important, they primarily evaluate whether a model can produce or manipulate programmatic artifacts, not whether it can reason about the principles that guide design decisions. Computer architecture plays a different role in the computing stack: it serves as the vital interface between software and hardware to define how these complex pieces interact, where careful orchestration of system components and their trade-offs *informs and influences implementation*. These decisions rely on conceptual understanding and analytical reasoning that is guided by application workloads and technology trends, rather than just code synthesis. Importantly, the skills required by architects to navigate these multi-objective design space problems can be systematically evaluated through a question—answering (QA) paradigm.

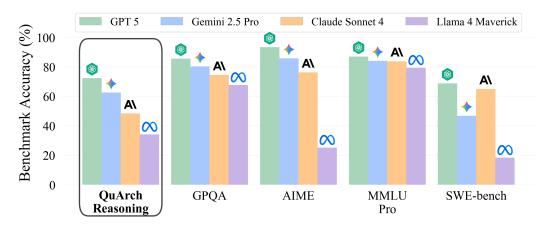

Figure 1: Reported results (Vals AI, Inc., 2025) for different models across QUARCH and multiple other SOTA benchmarks to date.

To this end, we introduce QUARCH: a question-answering benchmark to assess the architectural knowledge and reasoning capabilities of LLMs required in computing systems design. Figure 1 presents reported performance of frontier models across other reasoning domains in comparison to QUARCH, demonstrating that reasoning models are not yet able to solve advanced architecture questions. This gap underscores the need for focused evaluation on architectural reasoning to translate LLM progress into agentic methodologies that can accelerate innovation in computing systems.

QUARCH aims to capture the broad domain knowledge and skill set that architects possess by constructing the benchmark around four foundational competencies: Recall, Analyze, Design, and Implement. Existing computing systems benchmarks primarily target technical implementation skills (Table 1), but all four competencies—recalling foundational principles, analyzing workloads and constraints, designing systems that balance objectives, and implementing solutions via code—are complementary and critical for effective architecture design. Although we focus on computer architecture, these skills are broadly applicable to many systems tasks. Our framework enables systematic evaluation that holistically measures an agent's ability so that model progress can be measured with fine-grained skills and compared over time.

In summary, our work makes the following contributions: **1** OUARCH is the first benchmark designed to evaluate advanced computer architecture knowledge and reasoning in LLMs and is comprised of 2,671 expert-validated QAs. 1,124 questions were curated through academic crowdsourcing and community competitions, and 1,547 questions were synthetically generated and human-verified. 2 To promote holistic evaluation of AI agents for systems tasks, we formalize a skills framework to systematically assess 10 frontier models on QUARCH. Our evaluation reveals that even flagship LLMs today struggle with skills requiring higher-order thinking. Notably, QUARCH uncovers a significant performance gap between LLMs' architectural knowledge and reasoning abilities. 3 We conduct an in-depth analysis to offer key insights and observations on model trends and failure points. This includes incorrect architectural assumptions made, difficulties with modeling system state, absence of architecture-semantics in code execution, and heterogeneity in LLM topic expertise. 4 We establish a trustworthy and scalable methodology for evaluating the correctness of free-form responses in QUARCH by comparing LLM judgments with human domain-expert verdicts across 100 OAs and 10 frontier models. We show that LLM judgments agree with human experts at a rate of 85.35%, which is comparable to human-human grading agreement rates of 90.7% on the QUARCH benchmark.

#### 2 QuArch

#### 2.1 TOWARDS AGENTIC SYSTEMS DESIGN: BUILDING AN AI ARCHITECT

**Skill Requirements.** To systematically assess progress towards agentic design of computing systems, we first introduce a conceptual framework to decompose the fundamental skills that computer

Table 1: ML benchmarks & datasets across the computing stack. QUARCH broadens the scope of current benchmarks by focusing on conceptual and analytical reasoning skills required for computer architecture and systems design. Benchmarks above QUARCH target more software-oriented tasks, while those below focus on more hardware-centric, chip design tasks.

| Benchmark & Dataset<br>for Computing Systems | Focus in<br>Computing Stack | Conceptual & Analytical QA | Design QA &<br>Program Impl. | Multimodal<br>Assessment | Expert<br>Verified | Benchmark<br>Size |

|----------------------------------------------|-----------------------------|----------------------------|------------------------------|--------------------------|--------------------|-------------------|

| SWE-bench (Jimenez et al., 2023)             | Software Eng.               | Х                          | ✓                            | Х                        | Х                  | 2294              |

| SWE-bench Verified (OpenAI, 2024)            | Software Eng.               | ×                          | ✓                            | ×                        | ✓                  | 500               |

| SWE-Perf (He et al., 2025)                   | Performance Eng.            | ×                          | ✓                            | ×                        | X                  | 140               |

| KernelBench (Ouyang et al., 2025)            | Performance Eng.            | ×                          | ✓                            | ×                        | X                  | 250               |

| CodeMMLU (Nguyen et al., 2025)               | Code Reasoning              | ✓                          | ×                            | ×                        | X                  | 19912             |

| CRUXEval (Gu et al., 2024)                   | Code Reasoning              | ✓                          | ✓                            | ×                        | X                  | 800               |

| QUARCH (This Work)                           | Architecture                | ✓                          | ✓                            | ✓                        | ✓                  | 2671              |

| SLDB (Alvanaki et al., 2025)                 | System Design               | Х                          | ✓                            | Х                        | ✓                  | 10                |

| CreativEval (DeLorenzo et al., 2024b)        | HW Design                   | ×                          | ✓                            | ×                        | X                  | 120               |

| VerilogEval (Liu et al., 2023b)              | RTL Generation              | ×                          | ✓                            | ×                        | X                  | 156               |

| CVDP (Pinckney et al., 2025b)                | RTL Generation              | ✓                          | ✓                            | ×                        | ✓                  | 783               |

| MG-Verilog (Zhang et al., 2024)              | RTL Generation              | ×                          | ✓                            | ×                        | X                  | 11000             |

| EDA Corpus (Wu et al., 2024a)                | EDA Tooling                 | ✓                          | ✓                            | ×                        | ✓                  | 1533              |

| FIXME (Wan et al., 2025)                     | Verification                | ×                          | ✓                            | ×                        | X                  | 180               |

| ChiPBench (Wang et al., 2024b)               | Layout                      | ×                          | ✓                            | ×                        | X                  | 20                |

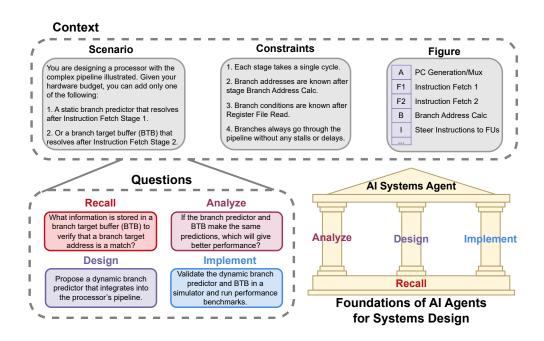

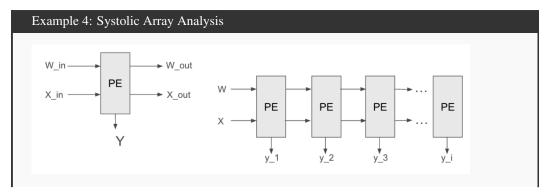

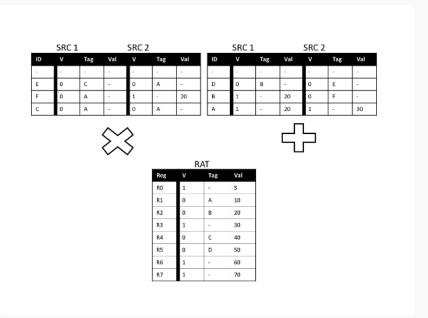

architects (and systems engineers more broadly) require. Figure 2 illustrates these skills: within a single problem scenario, we exemplify how different styles of QAs exercise different skills, from recall of fundamental domain knowledge to more advanced analysis, design, and implementation.

Recall: Retrieving domain knowledge, definitions, and facts. "What information is stored in a branch target buffer (BTB) to verify that a branch target address is a match?" This includes the ability to identify components and roles in a diagram or specification such as standard digital logic elements. Critically, domain knowledge underpins advanced reasoning (Krieger, 2004; Duncan, 2007).

Analyze: Deducing, inferring, calculating, or interpreting data and information from a scenario to reason about workload implications and system behavior. Identifying bottlenecks and being able to explain "why" is critically important for deeper understanding. "If the branch predictor and BTB make the same predictions, which will give better performance?"

Design: Proposing, inventing, or improving an architectural feature (method, component, or policy) while satisfying system requirements and constraints. It requires balancing nuanced performance, power, area, and cost trade-offs. Synthesizing a design often can require iterating over architectural block diagrams and system specifications. "Suggest a dynamic branch predictor that integrates into the processor's pipeline."

*Implement*: Translating a design into executable artifacts (e.g., code/RTL/simulation scripts). Typically, this skill is used to validate a solution via modeling or measurement. "*Implement the dynamic branch predictor and BTB in a simulator and run performance benchmarks.*"

Crucially, all of these skills are significant pillars exercised in different scenarios at different times by architects and systems engineers, with domain knowledge being the foundation upon which other higher-order skills can be built. For example, without first knowing the basics of how processor execution, memory hierarchy, concurrency, parallelism, and communication work, it is difficult (if not impossible) to reason about design and performance trade-offs within a complex multi-core system.

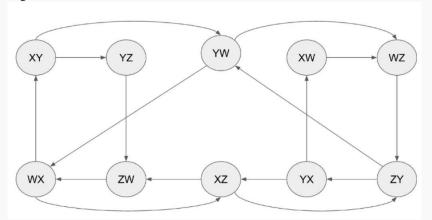

Knowledge Breadth Requirements. Computer architecture contains a multitude of specialized areas. Historically, architects focused on microprocessor design but expanded towards many-core systems and domain-specific accelerators (Blake et al., 2009; Dally et al., 2020) due to memory and power walls (Wulf & McKee, 1995; Esmaeilzadeh et al., 2011). Consequently, this elevated the importance of understanding memory systems, interconnects, and system-level methodology (Sangiovanni-Vincentelli, 2007; Carloni, 2015) to first-class concerns. Effective architecture and system design requires understanding relationships across these areas and reasoning about how they interact. For example, a processor aggressively optimized without considering the connected memory subsystem will exhibit more performance bottlenecks than if the two were optimized together. Thus, a benchmark should capture topic breadth to properly assess architectural knowledge.

Figure 2: QUARCH QA Skills Framework. The benchmark evaluates four complementary competencies: Recall, Analyze, Design, and Implement. QAs in QUARCH contain relevant context describing the scenario, constraints, and figures when appropriate. The illustrative example shows how distinct question styles derived from the same context can probe different skills. Together, these competencies form the building blocks required for systems design in computer architecture. Balanced mastery of skills will enable more effective agents and workflows across the computing stack.

#### 2.2 BENCHMARK CONSTRUCTION

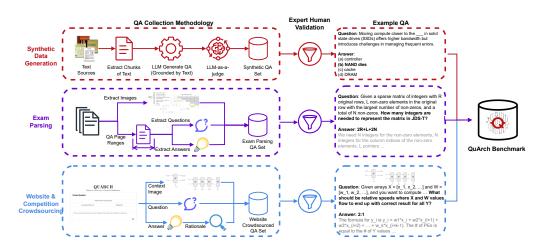

Curating a computer-architecture benchmark is particularly difficult because high-quality, openly usable sources are scarce relative to other domains (Reddi & Yazdanbakhsh, 2025) and authoring or validating benchmark entries requires substantial domain expertise to ensure technical correctness. We adopt a three-pronged strategy that combines synthetic data generation, academic exams, and expert crowdsourcing and competitions (Fig. 3). Every QA is reviewed and expert-validated by doctoral students with graduate-level training in computer architecture before inclusion in QUARCH.

**Synthetic Data Generation.** We collected open-source materials to curate a large corpus of computer architecture knowledge spanning technical manuals, academic publications, and comprehensive online resources. This corpus reflects a diverse and thorough survey of publicly available knowledge in the field and serves as a foundation for QUARCH. Using this corpus, LLMs generated cloze-style multiple-choice QAs (Rogers et al., 2023) to balance educational value with practical assessment. QAs then underwent two-stage validation: LLM-as-a-judge (Zheng et al., 2023) for initial filtering (as these cloze-style QAs naturally involve little reasoning) followed by independent review of each QA by three experts. This approach enabled the identification and removal of questions lacking definitive answers or those too narrowly scoped for meaningful assessment. Prompt details are in Appendix D.6 and D.7, .

**Expert Crowdsourcing & Competitions.** We developed a web-based portal specifically for crowd-sourcing architectural reasoning questions to target more advanced analysis, design, and implementation skills that are difficult to synthetically generate. QAs were collected via an open submission platform for individuals with technical backgrounds and time-boxed competitions. Similar to other recent benchmark curation methodologies such as Humanity's Last Exam (Phan et al., 2025), the interactive portal provided exemplary reasoning examples and real-time feedback on submitted questions to encourage participants to submit challenging questions and a solution rationale (Ap-

Figure 3: We construct QUARCH with a three-pronged approach including a blend of synthetic data generation, community crowdsourcing, and academic exams. All QAs are validated by a human expert to curate QUARCH's final benchmark set of 2,671 question-answer pairs.

pendix B.1). The individual submissions and competition submissions underwent expert review to check for ambiguity and correctness before final acceptance.

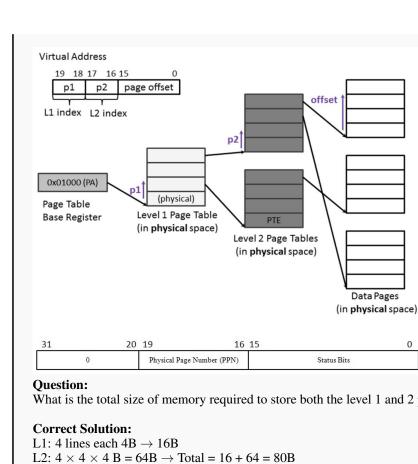

Academic Exams. We additionally curated QAs from university computer-architecture exams obtained via our community crowdsourcing process and manual web scraping. A custom pipeline was developed to convert PDFs into standalone QAs. Llamaparse was first used to extract diagrams (LlamaIndex, 2025). An LLM then segmented the exam into per-question PDFs to decompose the large exam PDF and parse each QA into context, question, and solution fields. To verify parsing, QAs underwent similar two-stage validation as our synthetic data generation process that employed LLM-as-a-judge for initial filtering followed by expert review. This pipeline yielded exam-level, multimodal QAs suitable for benchmarking. Prompt details for this pipeline are in Appendix D.8, D.9, and D.10.

#### 2.3 BENCHMARK CHARACTERIZATION

We characterize QUARCH's 2,671 QA pairs along architecture topics, skill focus, question format, and modality, establishing a framework for fine-grained tracking of benchmark growth over time.

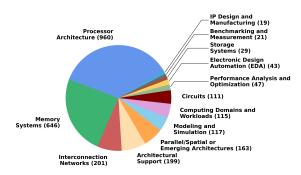

Architecture Topic Diversity. QUARCH captures diverse topics in 13 core areas derived from key themes in modern computer architecture research (Figure 4). Processor architecture accounts for the largest proportion of QAs (37%), followed by memory systems (25%) and interconnection networks (8%). This distribution mirrors the field's current and historical emphasis, with niche areas containing fewer QAs. pendix C provides example QAs that show the breadth and depth of topics covered in QUARCH. The topic distribution was estimated via two-stage classification using a text embedding model and LLM labeling (Appendix D.5).

Figure 4: Distribution of topics in QUARCH.

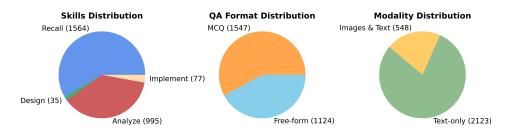

**Skills Coverage.** Figure 5 characterizes QAs by the skills in Sec. 2.1, derived from LLM labeling (Appendix D.4) with examples for each given in Appendix C.1. In particular, QUARCH targets advanced reasoning by providing nearly 1000 analysis QAs and  $\sim$ 100 design & implementation

Figure 5: Breakdown of skill, format, and modality distributions in QUARCH.

QAs. This disparity in number reflects the intrinsic difficulty of authoring and validating design & implementation QAs, mirroring their natural frequency in our sources (e.g., exams typically have few design QAs relative to analysis). We term *recall-focused* QAs QUARCH-RECALL and *higher-order skill* QAs (e.g., analyze, design, implement) QUARCH-REASONING.

Question Format and Input Modalities. In line with prior QA and code-reasoning benchmarks (Rein et al., 2023; Hendrycks et al., 2020; Nguyen et al., 2025), QUARCH includes 1,547 multiple-choice questions (MCQs), which are amenable to synthetic generation (Section 2.2) and have clear evaluation criteria. However, academic evaluation of domain-expert architecture knowledge is highly open-ended in structure, requiring deeper critical thinking, and thus cannot be formulated as MCQs. QUARCH therefore includes 1,124 free-response questions (FRQ), with examples in Appendix C. Furthermore, QUARCH contains both 2,123 text-only and 548 multimodal (images & text) questions. These multimodal examples assess image interpretation and reasoning capabilities on structured and spatial information, such as architecture datapath diagrams, circuit schematics, pipeline timing charts, roofline performance plots, and specification tables.

#### 3 EXPERIMENTAL SETUP

**Models.** We evaluate ten frontier models from Alibaba Cloud, Anthropic, DeepSeek, Google, Meta, Mistral, and OpenAI on QUARCH across the four skills (Recall, Analyze, Design, Implement) presented in Section 2.1. Evaluation results for an additional 16 models are reported in Appendix B.4.

**Evaluation grading.** All models are evaluated in a zero-shot setting. Full evaluation prompts are provided in Appendix D. For MCQ-style responses, models must conclude with the correct choice of A, B, C, or D. For FRQ-style questions, we employ LLM-as-a-judge (Zheng et al., 2023), tasking an external model to assess the correctness of an answer with respect to the ground truth. We further motivate and rigorously validate our use of LLM-as-a-judge in Section 4.4.

**Metrics.** For both MCQ- and FRQ-style questions, we report model performance using "pergeneration accuracy", the percentage of correct answers received out of n total responses, to provide a better estimate of the pass@k=1 metric (Pinckney et al., 2025a) under stochastic generation parameters. In all evaluations, we generate n=3 samples per question.

#### 4 EVALUATION & ANALYSIS

#### 4.1 MODEL PERFORMANCE

Table 2 reports headline accuracy of 10 frontier models on QUARCH. As defined in Section 2.3, QUARCH-REASONING covers higher-order skills in our framework, while QUARCH-RECALL captures domain-knowledge retrieval (rather than reasoning). QUARCH-RECALL performance is consistently strong across all frontier models. Including a recall split is useful to establish a baseline in a field that lacks a dedicated benchmark: the split distinguishes "don't know" from "can't reason," and informs whether fundamental domain knowledge is present in models. Unlike frontier models, current Small Language Models (SLMs) exhibit gaps on recall performance (Appendix B.3). Overall, the reasoning variant of GPT-5 leads on QUARCH today with Gemini models forming the next tier. We note that GPT-OSS 120B and DeepSeek R1 are evaluated only on text (no images), so their scores reflect text-only capability. We focus the rest of our analysis on QUARCH-REASONING because it offers the most headroom for today's frontier models to improve.

Table 2: Frontier model performance on QUARCH. Reported values are the per-generation accuracy across 3 generations. All models struggle much more on QUARCH-REASONING compared to QUARCH-RECALL. We highlight the first, second, and third best performing models.

| Model                      | QuArch-Recall | QUARCH-REASONING | Δ     |

|----------------------------|---------------|------------------|-------|

| Multimodal Models          |               |                  |       |

| GPT-5                      | 89.0          | 72.4             | -16.5 |

| GPT-5 (Non-Reasoning)      | 86.3          | 49.0             | -37.3 |

| Gemini 2.5 Pro             | 87.4          | 62.9             | -24.5 |

| Gemini 2.5 Flash           | 83.4          | 56.8             | -26.6 |

| Claude Sonnet 4            | 85.5          | 48.4             | -37.0 |

| Claude 3.7 Sonnet Thinking | 85.8          | 52.1             | -33.7 |

| Llama 4 Maverick           | 85.3          | 34.2             | -51.1 |

| Mistral Medium 3.1         | 84.5          | 34.1             | -50.4 |

| Text-Only Models           |               |                  |       |

| GPT-OSS 120B               | 84.2          | 64.7             | -19.5 |

| DeepSeek R1                | 86.9          | 56.1             | -30.7 |

#### 4.2 SKILL PERFORMANCE TRENDS

Table 3 provides fine-grained skill-wise performance across models, with key trends shared below:

- (1) Recall is Mastered, Higher-Order Skills are Not. Frontier models have largely mastered recall, but fall short on advanced skills. Recall accuracy ranges between 83%-89%, suggesting architectural knowledge is present. However, analyze, design, and implement skills are lower than recall by 32.1%, 39.2%, and 38.2% on average respectively. Notably, multiple models with strong recall accuracy fall below 35% on other skills (e.g., Llama 4 Maverick, Mistral Medium 3.1). In particular, design skills exhibit the widest performance gaps, ranging between 18-87%. This suggests the design QAs, despite comprising a small proportion of the dataset, provide a strong discriminative signal that correlates with performance across the full QUARCH benchmark.

- (2) Reasoning Matters for Advanced Skills. Results from (1) indicate that translating domain knowledge into advanced skills will require targeted training and test-time deliberation mechanisms. Comparison of GPT-5-thinking with its non-reasoning variant supports this. GPT-5 outperforms by 23%, 34%, and 30% on analyze, design, and implement QAs respectively, compared to a much smaller 3% lift on recall QAs. Moreover, GPT-5 stands as an extreme outlier on design QAs at 89%, suggesting its training corpora and test-time reasoning budget better capture the skills needed to select and justify design decisions under constraints compared to other frontier models.

- (3) Variations in Competencies Across Models. Our skill framework exposes model-specific strengths and failures that a single aggregate score hides. Overall, 23 of the 26 models evaluated (Appendix B.3) score lower on either analysis or design QAs than on implementation QAs, underscoring the need to target all of these higher-order skills to holistically assess architecture competency.

#### 4.3 KEY INSIGHTS & OBSERVATIONS

Results on QUARCH illustrate a clear gap in model capabilities. Based on extensive grading performed by experts (Section 4.4), we synthesize key insights into specific failure modes observed.

- (1) Struggles with architecture-semantics of code execution. Architectural semantics of code execution refers to the deep understanding of how high-level code interacts with the underlying hardware architecture (e.g., memory access patterns, instruction scheduling, etc.) (Tschand et al., 2025). Our analysis reveals that LLMs struggle with these nuanced aspects of code execution, failing to accurately predict or analyze the architectural implications of code snippets (Appendix C.2).

- (2) Assuming unconventional architectural properties. In computer architecture, decades of practice have cemented certain system designs, such as byte-addressable memory, as de facto defaults unless otherwise specified. However, our analysis exposes a misalignment: when prompts fail to state conventions explicitly, we observe LLMs defaulting to unconventional choices, such as word-level addressing (Appendix C.3). Models are able to succeed when provided with the default con-

Table 3: Per-generation accuracy (%) by QuArch Skill. Best performing models in each category highlighted first, second, and third.

| Model                      | QuArch-Reasoning |         |             |             |

|----------------------------|------------------|---------|-------------|-------------|

|                            | Recall           | Analyze | Design      | Implement   |

| Multimodal Models          |                  |         |             |             |

| GPT-5                      | 89.0             | 72.1    | 86.7        | 71.0        |

| GPT-5 (Non-Reasoning)      | 86.3             | 49.5    | 52.4        | 40.7        |

| Gemini 2.5 Pro             | 87.4             | 63.3    | <b>59.0</b> | <b>59.7</b> |

| Gemini 2.5 Flash           | 83.4             | 57.3    | <b>57.1</b> | 49.8        |

| Claude Sonnet 4            | 85.5             | 49.0    | 36.2        | 46.8        |

| Claude 3.7 Sonnet Thinking | 85.8             | 53.3    | 34.3        | 45.5        |

| Llama 4 Maverick           | 85.3             | 35.1    | 18.1        | 30.2        |

| Mistral Medium 3.1         | 84.5             | 34.8    | 27.6        | 27.7        |

| Text-only Models           |                  |         |             |             |

| GPT-OSS 120B               | 84.2             | 65.5    | 56.1        | 57.8        |

| DeepSeek R1                | 86.9             | 57.4    | 38.6        | 47.1        |

ventions explicitly, highlighting that practitioners leveraging LLMs in this domain must identify their implicit assumptions to guide the model effectively.

- (3) Modeling and tracking system state. Building an intuition and mental model of how system components interact and the implications of their interactions is central to computer architecture. In general-domain QA, this corresponds to situational world modeling (Rogers et al., 2023): instantiating entities, tracking their locations and states, and inferring temporal and causal relations to answer queries about an evolving scenario. We find that frontier models often fail to maintain consistent system state and thus misunderstand how local actions cascade into system-level effects on latency, throughput, and correctness (Appendix C.4).

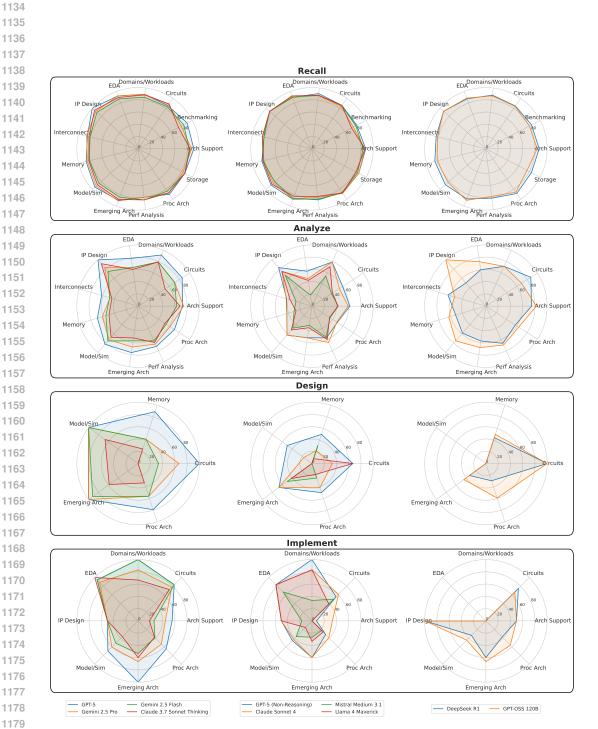

- (4) Variations in domain expertise. Our analysis reveals that LLMs develop specialized expertise across different domains. For instance, within "Implement"-Style questions, Llama 4 Maverick performs well on Computing Domains & Workloads and struggles on Modeling & Simulation, while Mistral Medium 3.1 exhibits the opposite behavior. Importantly, Llama 4 Maverick and Mistral Medium 3.1 overall performed similarly on "Implement"-Style questions, suggesting model capabilities are more nuanced than the aggregate scores of Table 3. These findings provide the opportunity to create multi-model systems that combine the domain strengths of multiple LLMs rather than relying on a single "best" model. Spider plots visualizing these per-topic variations for all frontier models across all skills are shown in Appendix B.2.

- (5) Sensitivity to QA modality. In computer architecture, visuals such as pipeline diagrams, cache hierarchies, and system interconnects convey structural relationships and spatial information that cannot be adequately captured through text descriptions alone (Chang et al., 2024a). Multimodal models exhibit an average 6% drop in accuracy from text-only free-response to image-only free-response questions (Appendix Table 6). This gap indicates that frontier models struggle with interpreting and reasoning about diagrams, schematics, and tables (see Appendix C.5 for failure examples).

#### 4.4 LLM-AS-A-JUDGE ANALYSIS

**Motivation.** Semantically equivalent and correct solutions to the same FRQ can differ in phrasing, as shown in Appendix C.6. Since full manual grading by domain experts is intractable, we employ LLM-as-a-judge for QUARCH.

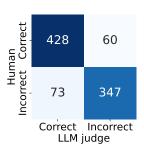

**Human Validation.** While LLM-as-a-judge has gained popularity for evaluating FRQ-style questions (Lee et al., 2024; Zhou et al., 2023; Mañas et al., 2024; Pinckney et al., 2025b), the approach is still relatively new. We therefore validate the fidelity of LLM-as-a-Judge by measuring agreement rates between human expert and LLM judge verdicts on the correctness of generated FRQ responses. We randomly sampled 100 (8.9%) freeform QAs in QUARCH, and generated one response from the 10 models under evaluation in Sec. 4.1. We tasked a cohort of 11 domain experts

in computer architecture and hardware design to manually grade the resultant 908 responses<sup>1</sup> as CORRECT, PARTIALLY-CORRECT, or INCORRECT. For analysis purposes, PARTIALLY-CORRECT is recategorized as INCORRECT. Each question is graded independently by up to 3 experts and the majority consensus is taken. To control for LLM judge stochasticity, all judge evaluations in Sec. 4.1 and Appendix B.4 are likewise performed 3x and the majority vote taken.

LLM judges agree with human experts. We observe an agreement rate of 85.35% between LLM judges and humans (Fig. 6), when using Claude 3.7 Sonnet as the judge. We compare this agreement rate with the rate that expert humans disagree on verdicts. 84 of the 908 responses required a third expert to adjudicate between a correct and incorrect vote, corresponding to a human-to-human agreement rate of 90.7%. Since this agreement rate is broadly comparable to the frequency with which LLM-as-a-Judge consensus agrees with human consensus, we argue LLM-as-a-Judge is eminently suitable for scalable and informative benchmarking of model performance on QUARCH. Additional experiments on human expert grading difficulty, alternative LLMs as judges, and majority consensus rates are included in Appendix B.6

Figure 6: Confusion matrix comparing LLM-as-a-Judge with domainexpert human grading on FRQ.

### 5 RELATED WORK

**Software.** Function-level code efficiency benchmarks (Du et al., 2024; Huang et al., 2024; Shypula et al., 2024; Waghjale et al., 2024) and domain-focused performance tasks (Press et al., 2025; Ouyang et al., 2025) evaluate correctness-preserving edits and runtime gains at the function or kernel level. Repository-scale SWE benchmarks and agentic toolchains (Jimenez et al., 2024; Yang et al., 2024; Wang et al., 2025) test long-horizon code manipulation and integration. Recent QA code understanding benchmarks (Gu et al., 2024; Nguyen et al., 2025; Li et al., 2024; Dinella et al., 2024) target control/data-flow semantics, behavioral equivalence, and code review comprehension. Unlike QUARCH, which primarily targets pre-implementation, system, and architectural judgment, these works focus on code artifacts, assessing code semantics rather than system-level design.

Hardware. Domain-specific foundation models for chip design (Liu et al., 2023a), electronic design automation (EDA) tool interaction (Wu et al., 2024a;b), RTL generation (Chang et al., 2024b; Thakur et al., 2024; Liu et al., 2024; Blocklove et al., 2023), design optimization (Chang et al., 2023; Pei et al., 2024; DeLorenzo et al., 2024a), and security-oriented tasks (bug repair and assertions) (Tsai et al., 2024; Yao et al., 2024; Fu et al., 2023; Pearce et al., 2023; Nair et al., 2023; Meng et al., 2024; Mali et al., 2024) emphasize producing or improving implementation artifacts and driving tools. In contrast, QUARCH isolates the reasoning that guides implementation, testing whether models can reason about architectural principles and trade-offs, rather than their ability to generate HDL/RTL or steer EDA flows.

**QA benchmarks.** General-purpose and domain QA datasets (Rajpurkar et al., 2016; Trischler et al., 2016; Clark et al., 2019; Hendrycks et al., 2020; Rein et al., 2023; Huber et al., 2022; Jin et al., 2019; Cobbe et al., 2021; Zhong et al., 2020) have been instrumental for advancing and measuring LLMs (Rogers et al., 2023). QUARCH targets advancing computer architecture specifically, with expert-verified items and skill-wise evaluation capabilities not covered by existing QA benchmarks.

#### 6 CONCLUSION

We introduce QUARCH, the first benchmark to directly assess computer architecture knowledge and reasoning in LLMs across four complementary skills: Recall, Analyze, Design, and Implement. Evaluating ten frontier models on 2,671 expert-validated QAs, we find consistently strong recall across models but reveal a pronounced gap in higher-order abilities that demand architectural reasoning. By providing insights into failure modes and enabling systematic tracking, QUARCH lays the groundwork for accelerating AI progress in computer architecture and, more broadly, in reasoning-centric skills for systems design.

<sup>&</sup>lt;sup>1</sup>Non-multimodal models cannot generate responses for the multimodal proportion of sampled questions.

### **ETHICS STATEMENT**

QUARCH was curated from sources that permit academic use and redistribution. Synthetic items were generated from a domain corpus compiled from public materials, exam-derived items were collected from publicly accessible university course pages or contributed by instructors, and crowd-sourced items were submitted through our portal with explicit contributor consent. All expert validators who participated in question review and acceptance are co-authors of this paper. We did not recruit paid crowd workers; when individuals submitted questions via our portal, they consented to inclusion under our dataset license and to public attribution (or opted to remain anonymous). We do not collect personally identifying information beyond optional contact details for acknowledgment. No student data or private repositories were used. Where third-party figures or excerpts are included, we respect the original licenses and provide attribution. We will honor takedown requests for any inadvertently mislicensed content. This project did not involve human-subject experiments or interventions and, to the best of our understanding, does not require IRB oversight.

#### REPRODUCIBILITY STATEMENT

Section 2.2 describes the methodology for constructing QUARCH that can be used to reproduce a dataset of similar quality and characteristics. Appendix D.8, D.9, and D.10 each expand on the details of the methodology overview provided in Section 2.2. Additionally, exact prompts used for evaluation results are documented in Appendix D.1, D.2, D.3, and D.4 for reproducibility.

#### REFERENCES

- Elisavet Lydia Alvanaki, Kevin Lee, and Luca P Carloni. Sldb: An end-to-end heterogeneous system-on-chip benchmark suite for llm-aided design. In 2025 IEEE International Conference on LLM-Aided Design (ICLAD), pp. 227–234. IEEE, 2025.

- Geoffrey Blake, Ronald G. Dreslinski, and Trevor Mudge. A survey of multicore processors. *IEEE Signal Processing Magazine*, 26(6):26–37, 2009. doi: 10.1109/MSP.2009.934110.

- Jason Blocklove, Siddharth Garg, Ramesh Karri, and Hammond Pearce. Chip-chat: Challenges and opportunities in conversational hardware design. In 2023 ACM/IEEE 5th Workshop on Machine Learning for CAD (MLCAD), pp. 1–6. IEEE, 2023.

- Luca P. Carloni. From latency-insensitive design to communication-based system-level design. *Proceedings of the IEEE*, 103(11):2133–2151, 2015. doi: 10.1109/JPROC.2015.2480849.

- Kaiyan Chang, Ying Wang, Haimeng Ren, Mengdi Wang, Shengwen Liang, Yinhe Han, Huawei Li, and Xiaowei Li. Chipgpt: How far are we from natural language hardware design. *arXiv* preprint *arXiv*:2305.14019, 2023.

- Kaiyan Chang, Zhirong Chen, Yunhao Zhou, Wenlong Zhu, Kun Wang, Haobo Xu, Cangyuan Li, Mengdi Wang, Shengwen Liang, Huawei Li, et al. Natural language is not enough: Benchmarking multi-modal generative ai for verilog generation. In *Proceedings of the 43rd IEEE/ACM International Conference on Computer-Aided Design*, pp. 1–9, 2024a.

- Kaiyan Chang, Zhirong Chen, Yunhao Zhou, Wenlong Zhu, Haobo Xu, Cangyuan Li, Mengdi Wang, Shengwen Liang, Huawei Li, Yinhe Han, et al. Natural language is not enough: Benchmarking multi-modal generative ai for verilog generation. *arXiv preprint arXiv:2407.08473*, 2024b.

- Christopher Clark, Kenton Lee, Ming-Wei Chang, Tom Kwiatkowski, Michael Collins, and Kristina Toutanova. Boolq: Exploring the surprising difficulty of natural yes/no questions. *arXiv* preprint *arXiv*:1905.10044, 2019.

- Karl Cobbe, Vineet Kosaraju, Mohammad Bavarian, Mark Chen, Heewoo Jun, Lukasz Kaiser, Matthias Plappert, Jerry Tworek, Jacob Hilton, Reiichiro Nakano, Christopher Hesse, and John Schulman. Training Verifiers to Solve Math Word Problems, November 2021.

- William J Dally, Yatish Turakhia, and Song Han. Domain-specific hardware accelerators. *Communications of the ACM*, 63(7):48–57, 2020.

- Matthew DeLorenzo, Animesh Basak Chowdhury, Vasudev Gohil, Shailja Thakur, Ramesh Karri, Siddharth Garg, and Jeyavijayan Rajendran. Make every move count: Llm-based high-quality rtl code generation using mcts. *arXiv preprint arXiv:2402.03289*, 2024a.

- Matthew DeLorenzo, Vasudev Gohil, and Jeyavijayan Rajendran. Creativeval: Evaluating creativity of Ilm-based hardware code generation. *arXiv* preprint arXiv:2404.08806, 2024b.

- Elizabeth Dinella, Satish Chandra, and Petros Maniatis. Crqbench: A benchmark of code reasoning questions. *arXiv preprint arXiv:2408.08453*, 2024. doi: 10.48550/arXiv.2408.08453. URL https://arxiv.org/abs/2408.08453.

- Mingzhe Du, Anh Tuan Luu, Bin Ji, Qian Liu, and See-Kiong Ng. Mercury: A code efficiency benchmark for code large language models. In *NeurIPS Datasets and Benchmarks*, 2024. URL https://arxiv.org/abs/2402.07844.

- Ravit Golan Duncan. The role of domain-specific knowledge in generative reasoning about complicated multileveled phenomena. *Cognition and Instruction*, 25(4):271–336, 2007.

- Hadi Esmaeilzadeh, Emily Blem, Renee St. Amant, Karthikeyan Sankaralingam, and Doug Burger. Dark silicon and the end of multicore scaling. In *Proceedings of the 38th annual international symposium on Computer architecture*, pp. 365–376, 2011.

- Weimin Fu, Kaichen Yang, Raj Gautam Dutta, Xiaolong Guo, and Gang Qu. Llm4sechw: Leveraging domain-specific large language model for hardware debugging. In 2023 Asian Hardware Oriented Security and Trust Symposium (AsianHOST), pp. 1–6. IEEE, 2023.

- Alex Gu, Baptiste Roziere, Hugh James Leather, Armando Solar-Lezama, Gabriel Synnaeve, and Sida Wang. Cruxeval: A benchmark for code reasoning, understanding and execution. In *Proceedings of the 41st International Conference on Machine Learning (ICML)*, volume 235 of *Proceedings of Machine Learning Research*, pp. 16568–16621. PMLR, July 2024. URL https://proceedings.mlr.press/v235/gu24c.html.

- Xinyi He, Qian Liu, Mingzhe Du, Lin Yan, Zhijie Fan, Yiming Huang, Zejian Yuan, and Zejun Ma. Swe-perf: Can language models optimize code performance on real-world repositories? *arXiv* preprint arXiv:2507.12415, 2025.

- Dan Hendrycks, Collin Burns, Steven Basart, Andy Zou, Mantas Mazeika, Dawn Song, and Jacob Steinhardt. Measuring massive multitask language understanding. *arXiv preprint arXiv:2009.03300*, 2020.

- Dong Huang, Yuhao Qing, Weiyi Shang, Heming Cui, and Jie M. Zhang. Effibench: Benchmarking the efficiency of automatically generated code. In *NeurIPS Datasets and Benchmarks*, 2024. URL https://arxiv.org/abs/2402.02037.

- Patrick Huber, Armen Aghajanyan, Barlas Oguz, Dmytro Okhonko, Scott Yih, Sonal Gupta, and Xilun Chen. CCQA: A New Web-Scale Question Answering Dataset for Model Pre-Training. In Marine Carpuat, Marie-Catherine de Marneffe, and Ivan Vladimir Meza Ruiz (eds.), *Findings of the Association for Computational Linguistics: NAACL 2022*, pp. 2402–2420, Seattle, United States, July 2022. Association for Computational Linguistics. doi: 10.18653/v1/2022. findings-naacl.184.

- Carlos E Jimenez, John Yang, Alexander Wettig, Shunyu Yao, Kexin Pei, Ofir Press, and Karthik Narasimhan. Swe-bench: Can language models resolve real-world github issues? *arXiv preprint arXiv:2310.06770*, 2023.

- Carlos E Jimenez, John Yang, Alexander Wettig, Shunyu Yao, Kexin Pei, Ofir Press, and Karthik R Narasimhan. SWE-bench: Can language models resolve real-world github issues? In *The Twelfth International Conference on Learning Representations*, 2024. URL https://openreview.net/forum?id=VTF8yNQM66.

Qiao Jin, Bhuwan Dhingra, Zhengping Liu, William Cohen, and Xinghua Lu. PubMedQA: A Dataset for Biomedical Research Question Answering. In Kentaro Inui, Jing Jiang, Vincent Ng, and Xiaojun Wan (eds.), *Proceedings of the 2019 Conference on Empirical Methods in Natural Language Processing and the 9th International Joint Conference on Natural Language Processing (EMNLP-IJCNLP)*, pp. 2567–2577, Hong Kong, China, November 2019. Association for Computational Linguistics. doi: 10.18653/v1/D19-1259.

- Stefan H Krieger. Domain knowledge and the teaching of creative legal problem solving. *Clinical L. Rev.*, 11:149, 2004.

- Seongyun Lee, Seungone Kim, Sue Park, Geewook Kim, and Minjoon Seo. Prometheus-vision: Vision-language model as a judge for fine-grained evaluation. In *Findings of the association for computational linguistics ACL 2024*, pp. 11286–11315, 2024.

- Linyi Li, Shijie Geng, Zhenwen Li, Yibo He, Hao Yu, Ziyue Hua, Guanghan Ning, Siwei Wang, Tao Xie, and Hongxia Yang. Infibench: Evaluating the question-answering capabilities of code large language models. In Advances in Neural Information Processing Systems 37 (NeurIPS 2024), Datasets and Benchmarks Track, 2024. URL https://proceedings.neurips.cc/paper\_files/paper/2024/hash/e888eb9400fe14bb70e057aald719188-Abstract-Datasets\_and\_Benchmarks\_Track.html.

- Mingjie Liu, Teodor-Dumitru Ene, Robert Kirby, Chris Cheng, Nathaniel Pinckney, Rongjian Liang, Jonah Alben, Himyanshu Anand, Sanmitra Banerjee, Ismet Bayraktaroglu, et al. Chipnemo: Domain-adapted llms for chip design. *arXiv preprint arXiv:2311.00176*, 2023a.

- Mingjie Liu, Nathaniel Pinckney, Brucek Khailany, and Haoxing Ren. Verilogeval: Evaluating large language models for verilog code generation. In 2023 IEEE/ACM International Conference on Computer Aided Design (ICCAD), pp. 1–8. IEEE, 2023b.

- Shang Liu, Wenji Fang, Yao Lu, Qijun Zhang, Hongce Zhang, and Zhiyao Xie. Rtlcoder: Outperforming gpt-3.5 in design rtl generation with our open-source dataset and lightweight solution. In 2024 IEEE LLM Aided Design Workshop (LAD), pp. 1–5. IEEE, 2024.

- LlamaIndex. Llamaparse: A genai-native document parsing platform. Software, 2025. URL https://cloud.llamaindex.ai/parse. Accessed: 2025-09-18.

- Bhabesh Mali, Karthik Maddala, Vatsal Gupta, Sweeya Reddy, Chandan Karfa, and Ramesh Karri. Chiraag: Chatgpt informed rapid and automated assertion generation. In 2024 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), pp. 680–683. IEEE, 2024.

- Oscar Mañas, Benno Krojer, and Aishwarya Agrawal. Improving automatic vqa evaluation using large language models. In *Proceedings of the AAAI Conference on Artificial Intelligence*, volume 38, pp. 4171–4179, 2024.

- Xingyu Meng, Amisha Srivastava, Ayush Arunachalam, Avik Ray, Pedro Henrique Silva, Rafail Psiakis, Yiorgos Makris, and Kanad Basu. Nspg: Natural language processing-based security property generator for hardware security assurance. In *Proceedings of the 61st ACM/IEEE Design Automation Conference*, pp. 1–6, 2024.

- Ivo Petrov Nikola Jovanović Martin Vechev Mislav Balunović, Jasper Dekoninck. Matharena: Evaluating Ilms on uncontaminated math competitions. https://matharena.ai/, 2025. SRI Lab, ETH Zurich.

- Madhav Nair, Rajat Sadhukhan, and Debdeep Mukhopadhyay. Generating secure hardware using chatgpt resistant to cwes. *Cryptology ePrint Archive*, 2023.

- Dung Manh Nguyen, Thang Chau Phan, Nam Le Hai, Tien-Thong Doan, Nam V. Nguyen, Quang Pham, and Nghi D. Q. Bui. Codemmlu: A multi-task benchmark for assessing code understanding & reasoning capabilities of codellms. In *International Conference on Learning Representations* (*ICLR*), 2025. URL https://openreview.net/forum?id=CahIEKCu5Q.

- OpenAI. Introducing swe-bench verified. Blog post, OpenAI, August 2024. URL https://openai.com/index/introducing-swe-bench-verified/. Updated February 24, 2025.

- Krista Opsahl-Ong, Michael J Ryan, Josh Purtell, David Broman, Christopher Potts, Matei Zaharia, and Omar Khattab. Optimizing instructions and demonstrations for multi-stage language model programs. *arXiv* preprint arXiv:2406.11695, 2024.

- Anne Ouyang, Simon Guo, Simran Arora, Alex L Zhang, William Hu, Christopher Ré, and Azalia Mirhoseini. Kernelbench: Can Ilms write efficient gpu kernels? *arXiv preprint arXiv:2502.10517*, 2025.

- Hammond Pearce, Benjamin Tan, Baleegh Ahmad, Ramesh Karri, and Brendan Dolan-Gavitt. Examining zero-shot vulnerability repair with large language models. In *2023 IEEE Symposium on Security and Privacy (SP)*, pp. 2339–2356. IEEE, 2023.

- Zehua Pei, Hui-Ling Zhen, Mingxuan Yuan, Yu Huang, and Bei Yu. Betterv: Controlled verilog generation with discriminative guidance. *arXiv preprint arXiv:2402.03375*, 2024.

- Long Phan, Alice Gatti, Ziwen Han, Nathaniel Li, Josephina Hu, Hugh Zhang, Chen Bo Calvin Zhang, Mohamed Shaaban, John Ling, Sean Shi, et al. Humanity's last exam. *arXiv* preprint *arXiv*:2501.14249, 2025.

- Nathaniel Pinckney, Christopher Batten, Mingjie Liu, Haoxing Ren, and Brucek Khailany. Revisiting verilogeval: A year of improvements in large-language models for hardware code generation. *ACM Transactions on Design Automation of Electronic Systems*, 2025a.

- Nathaniel Pinckney, Chenhui Deng, Chia-Tung Ho, Yun-Da Tsai, Mingjie Liu, Wenfei Zhou, Brucek Khailany, and Haoxing Ren. Comprehensive verilog design problems: A next-generation benchmark dataset for evaluating large language models and agents on rtl design and verification. *arXiv* preprint arXiv:2506.14074, 2025b.

- Ori Press, Brandon Amos, Haoyu Zhao, Yikai Wu, Samuel K. Ainsworth, Dominik Krupke, Patrick Kidger, Touqir Sajed, Bartolomeo Stellato, Jisun Park, Nathanael Bosch, Eli Meril, Albert Steppi, Arman Zharmagambetov, Fangzhao Zhang, David Perez-Pineiro, Alberto Mercurio, Ni Zhan, Talor Abramovich, Kilian Lieret, Hanlin Zhang, Shirley Huang, Matthias Bethge, and Ofir Press. Algotune: Can language models speed up general-purpose numerical programs?, 2025. URL https://arxiv.org/abs/2507.15887.

- Pranav Rajpurkar, Jian Zhang, Konstantin Lopyrev, and Percy Liang. SQuAD: 100,000+ Questions for Machine Comprehension of Text. In Jian Su, Kevin Duh, and Xavier Carreras (eds.), *Proceedings of the 2016 Conference on Empirical Methods in Natural Language Processing*, pp. 2383–2392, Austin, Texas, November 2016. Association for Computational Linguistics. doi: 10.18653/v1/D16-1264.

- Vijay Janapa Reddi and Amir Yazdanbakhsh. Architecture 2.0: Foundations of Artificial Intelligence Agents for Modern Computer System Design . *Computer*, 58(02):116-124, February 2025. ISSN 1558-0814. doi: 10.1109/MC.2024.3521641. URL https://doi.ieeecomputersociety.org/10.1109/MC.2024.3521641.

- David Rein, Betty Li Hou, Asa Cooper Stickland, Jackson Petty, Richard Yuanzhe Pang, Julien Dirani, Julian Michael, and Samuel R Bowman. Gpqa: A graduate-level google-proof q&a benchmark. *arXiv preprint arXiv:2311.12022*, 2023.

- Anna Rogers, Matt Gardner, and Isabelle Augenstein. Qa dataset explosion: A taxonomy of nlp resources for question answering and reading comprehension. *ACM Computing Surveys*, 55(10): 1–45, 2023.

- Alberto Sangiovanni-Vincentelli. Quo vadis, sld? reasoning about the trends and challenges of system level design. *Proceedings of the IEEE*, 95(3):467–506, 2007. doi: 10.1109/JPROC.2006. 890107.

- Alexander Shypula, Aman Madaan, Yimeng Zeng, Uri Alon, Jacob Gardner, Milad Hashemi, Graham Neubig, Parthasarathy Ranganathan, Osbert Bastani, and Amir Yazdanbakhsh. Learning performance-improving code edits. In *ICLR*, 2024. URL https://arxiv.org/pdf/2302.07867.

- Shailja Thakur, Baleegh Ahmad, Hammond Pearce, Benjamin Tan, Brendan Dolan-Gavitt, Ramesh Karri, and Siddharth Garg. Verigen: A large language model for verilog code generation. *ACM Transactions on Design Automation of Electronic Systems*, 29(3):1–31, 2024.

- Adam Trischler, Tong Wang, Xingdi Yuan, Justin Harris, Alessandro Sordoni, Philip Bachman, and Kaheer Suleman. Newsqa: A machine comprehension dataset. *arXiv preprint arXiv:1611.09830*, 2016.

- YunDa Tsai, Mingjie Liu, and Haoxing Ren. Rtlfixer: Automatically fixing rtl syntax errors with large language model. In *Proceedings of the 61st ACM/IEEE Design Automation Conference*, pp. 1–6, 2024.

- Arya Tschand, Muhammad Awad, Ryan Swann, Kesavan Ramakrishnan, Jeffrey Ma, Keith Lowery, Ganesh Dasika, and Vijay Janapa Reddi. Swizzleperf: Hardware-aware llms for gpu kernel performance optimization. *arXiv preprint arXiv:2508.20258*, 2025.

- Vals AI, Inc. Vals.ai benchmarks. https://www.vals.ai/benchmarks, 2025. Accessed: 2025-09-24.

- Siddhant Waghjale, Vishruth Veerendranath, Zora Zhiruo Wang, and Daniel Fried. ECCO: Can we improve model-generated code efficiency without sacrificing functional correctness? *arXiv*, 2024. URL https://arxiv.org/abs/2407.14044.

- Gwok-Waa Wan, Shengchu Su, Ruihu Wang, Qixiang Chen, Sam-Zaak Wong, Mengnv Xing, Hefei Feng, Yubo Wang, Yinan Zhu, Jingyi Zhang, et al. Fixme: Towards end-to-end benchmarking of llm-aided design verification. *arXiv preprint arXiv:2507.04276*, 2025.

- Xingyao Wang, Boxuan Li, Yufan Song, Frank F. Xu, Xiangru Tang, Mingchen Zhuge, Jiayi Pan, Yueqi Song, Bowen Li, Jaskirat Singh, Hoang H. Tran, Fuqiang Li, Ren Ma, Mingzhang Zheng, Bill Qian, Yanjun Shao, Niklas Muennighoff, Yizhe Zhang, Binyuan Hui, Junyang Lin, Robert Brennan, Hao Peng, Heng Ji, and Graham Neubig. Openhands: An open platform for AI software developers as generalist agents. In *The Thirteenth International Conference on Learning Representations*, 2025. URL https://openreview.net/forum?id=OJd3ayDDoF.

- Yubo Wang, Xueguang Ma, Ge Zhang, Yuansheng Ni, Abhranil Chandra, Shiguang Guo, Weiming Ren, Aaran Arulraj, Xuan He, Ziyan Jiang, et al. Mmlu-pro: A more robust and challenging multi-task language understanding benchmark. *arXiv preprint arXiv:2406.01574*, 2024a.

- Zhihai Wang, Zijie Geng, Zhaojie Tu, Jie Wang, Yuxi Qian, Zhexuan Xu, Ziyan Liu, Siyuan Xu, Zhentao Tang, Shixiong Kai, et al. Benchmarking end-to-end performance of ai-based chip placement algorithms. *arXiv preprint arXiv:2407.15026*, 2024b.

- Bing-Yue Wu, Utsav Sharma, Sai Rahul Dhanvi Kankipati, Ajay Yadav, Bintu Kappil George, Sai Ritish Guntupalli, Austin Rovinski, and Vidya A Chhabria. Eda corpus: A large language model dataset for enhanced interaction with openroad. *arXiv preprint arXiv:2405.06676*, 2024a.

- Haoyuan Wu, Zhuolun He, Xinyun Zhang, Xufeng Yao, Su Zheng, Haisheng Zheng, and Bei Yu. Chateda: A large language model powered autonomous agent for eda. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 2024b.

- Wm A Wulf and Sally A McKee. Hitting the memory wall: Implications of the obvious. *ACM SIGARCH computer architecture news*, 23(1):20–24, 1995.

- John Yang, Carlos E Jimenez, Alexander Wettig, Kilian Lieret, Shunyu Yao, Karthik R Narasimhan, and Ofir Press. SWE-agent: Agent-computer interfaces enable automated software engineering. In *The Thirty-eighth Annual Conference on Neural Information Processing Systems*, 2024. URL https://arxiv.org/abs/2405.15793.

- Xufeng Yao, Haoyang Li, Tsz Ho Chan, Wenyi Xiao, Mingxuan Yuan, Yu Huang, Lei Chen, and Bei Yu. Hdldebugger: Streamlining hdl debugging with large language models. *arXiv preprint* arXiv:2403.11671, 2024.

- Yongan Zhang, Zhongzhi Yu, Yonggan Fu, Cheng Wan, and Yingyan Celine Lin. Mg-verilog: Multi-grained dataset towards enhanced llm-assisted verilog generation. In 2024 IEEE LLM Aided Design Workshop (LAD), pp. 1–5. IEEE, 2024.

- Lianmin Zheng, Wei-Lin Chiang, Ying Sheng, Siyuan Zhuang, Zhanghao Wu, Yonghao Zhuang, Zi Lin, Zhuohan Li, Dacheng Li, Eric Xing, et al. Judging llm-as-a-judge with mt-bench and chatbot arena. *Advances in Neural Information Processing Systems*, 36:46595–46623, 2023.

- Haoxi Zhong, Chaojun Xiao, Cunchao Tu, Tianyang Zhang, Zhiyuan Liu, and Maosong Sun. JEC-QA: A Legal-Domain Question Answering Dataset. *Proceedings of the AAAI Conference on Artificial Intelligence*, 34(05):9701–9708, April 2020. ISSN 2374-3468. doi: 10.1609/aaai.v34i05. 6519

- Chunting Zhou, Pengfei Liu, Puxin Xu, Srinivasan Iyer, Jiao Sun, Yuning Mao, Xuezhe Ma, Avia Efrat, Ping Yu, Lili Yu, et al. Lima: Less is more for alignment. *Advances in Neural Information Processing Systems*, 36:55006–55021, 2023.

#### 810 APPENDIX 811 812 **Table of Contents** 813 815 816 817 В 818 **B**.1 **B.2** 819 B.3 820 **B.4** 821 **B.5** 822 **B.6** 823 824 825 $\mathbf{C}$ C.1 826 C.1.1827 C.1.2828 C.1.3829 C.1.4 830 831 832 C.2 C.2.1 833 C.2.2 834 C.2.3 835 C.2.4 836 837 838 C.3839 C.3.1C.3.2840 C.3.3841 842 843 C.4 844 C.4.1845 C.4.2846 847 C.5 848 C.5.1 849 C.5.2 850 851 C.6 852 853 D 854 D.1 855 D.2 LLM Prompt for MCQ Response ......53 856 D.3 LLM Prompt for FRQ LLM-as-a-Judge ......53 857 D.4 LLM Prompt for Skills Classification ......54 858 D.6 859 D.7 LLM Prompts for MCQ Filtering ......57 860 D.8 861 862 D.10

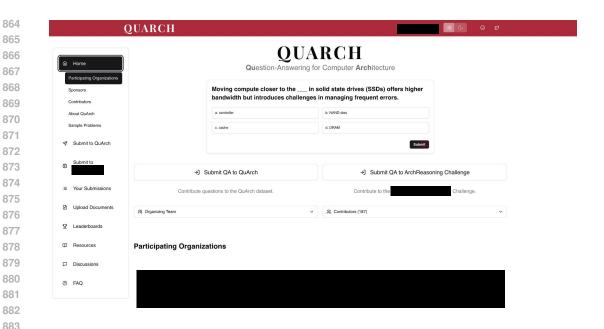

Figure 7: QuArch Website Home Page

#### A LLM USAGE

Language models were employed to refine the prose (e.g., grammar, clarity, and style) and to check formatting compliance with venue guidelines. Apart from their explicit roles described in the paper, namely for synthetic QA generation, exam parsing assistance, and evaluation (LLM-as-a-Judge), LLMs were not used to originate substantive scholarly content. All benchmark content admitted to the final release was verified by domain experts, and all prompts used in construction and evaluation are reported in Appendix D.

#### B ADDITIONAL RESULTS

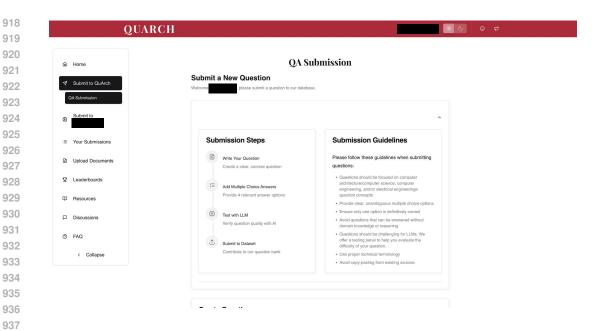

#### B.1 QUARCH CROWDSOURCING WEBSITE

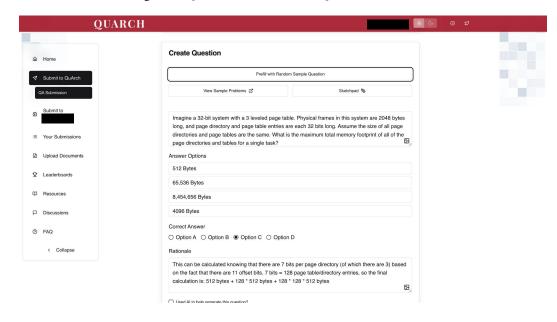

To provide a centralized location to crowdsource questions and exams, we created a QuArch website, shown in Figure 7. When a user wants to submit a question, they are presented with a set of instructions to guide accurate, relevant, and formatted questions, shown in Figure 8. Users submit the question, four answer options, the correct answer option, and a rationale for the correct answer, as shown in figure 9. While the user-submitted question is formatted by default in multiple-choice style, we instruct them to not submit questions where the correct answer is an "all of the above" or "none of the above." This enables us to concatenate the correct answer with the rationale and format the question as a free-response as well.

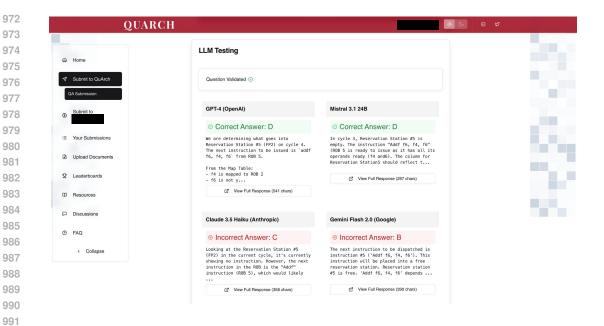

Once a question is written, we enable users to seamlessly test four non-frontier LLMs on correctness, shown in Figure 10. The question and potential answer choices is sent to the respective model within the MCQ Prompt shown in Appendix D.2. Users are presented with whether the model gets the question correct and its response. We explicitly do not want to give the users access to test their question on frontier LLMs to prevent them from overfitting to only specific LLMs. By giving users signal on whether non-frontier LLMs fail, they can create difficult and correct questions that

Figure 8: QuArch Website Submit Question Instructions

Figure 9: QuArch Website Submit Question Portal

Figure 10: QuArch Website LLM Testing on Question Submission

Figure 11: QuArch Website Question Submission Scoring

Figure 12: QuArch Website Admin Approvals

Figure 13: QuArch Website Exam Collection Portal

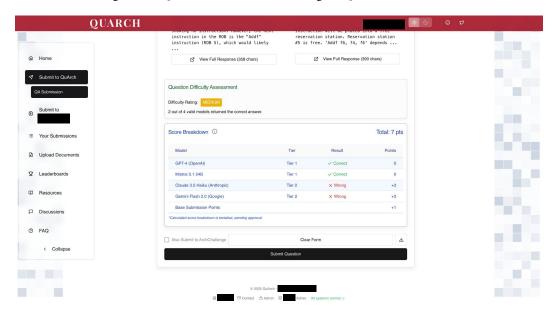

challenge a broad range of LLMs. The LLM performance is used to assign a score for the question, where making more frontier models fail corresponds to more points, shown in Figure 11. The website tracks submissions for each user, and we compile a leaderboard for users with the most cumulative points and question submissions.

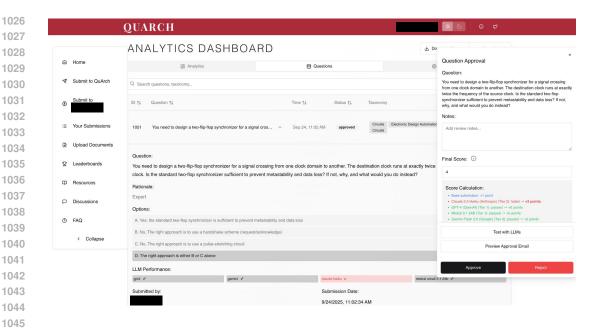

Once a question is submitted, we created an admin approval portal, shown in Figure 12. The approval process involves checking the questions for missing assumptions, poor relevance, or an insufficient rationale. Admins also reproduce each answer manually to ensure that the question-answer pair is objective and correct. Once a submission question is approved, it is added to the QUARCH benchmark set and the user that submitted the question is notified.

Lastly, users can also submit exams in the website, shown in Figure 13. We will then parse out the questions, context images, and answers from these computer architecture course exams using the offline methodology described in Sec. 2.2. Cumulatively, the questions collected from the QuArch crowdsourcing website are taxonomized by skill and funneled into the QUARCH-Reasoning benchmark.

#### B.2 TOPIC-WISE FURTHER CHARACTERIZATION

Figure 14 visualizes the topic-wise performance of the frontier models on QUARCH. As performance across all models on QUARCH-Recall is very high, very little topic-wise variability can be seen. However, in the higher-level skills (Analyze, Design, and Implement), models exhibit surprising heterogeneity in per-topic performance.

#### B.3 FULL MODEL RESULTS BY SKILL

Table 4 provides the complete set of results for all 26 evaluated models across the four skill categories in QUARCH. The table illustrates how models perform differently on factual recall compared to higher-order reasoning, design, and implementation. This comprehensive view allows for comparison across both small and large language models, highlighting overall trends and providing a foundation for tracking progress over time. While we do not discuss individual results here, the table captures the broader landscape of model performance and makes clear the varying degrees of capability across skills that are critical for computer architecture reasoning.

#### **Performance of Small Language Models**

Small language models (SLMs) keep pace with LLMs on recall-style questions, but their performance drops sharply on analyze, design, and implement tasks—especially when multimodal reasoning is required. This gap suggests that parameter scale (and associated capacity for long-horizon reasoning and state tracking) matters far more for higher-order architectural problem solving than for fact retrieval. In practice, SLMs are well-suited for low-latency, cost-efficient assistants that handle definitions, quick checks, and targeted lookups, while agentic systems design, trade-off analysis, and figure/table interpretation still benefit from larger models or strong tool scaffolding. A pragmatic path is a cascaded workflow: route recall to SLMs, escalate complex reasoning to LLMs, and bolster SLMs with retrieval and simulators rather than relying on scale alone.

We evaluate the performance of SLMs (defined as  $\leq 30B$  parameters) vs LLMs (defined as  $\geq 70B$  parameters or proprietary frontier models) on the taxonomy of QUARCH questions. SLMs exhibit a 13% drop in Recall accuracy, but a 27% drop on Analyze, 26% drop on Design, and 25% drop on Implement questions compared to LLMs. This indicates that while SLMs can replicate factual knowledge nearly as well as their larger counterparts, they falter on the higher-order reasoning and synthesis that are core to the field of computer architecture. These results imply that scaling up—or supplementing smaller models with external reasoning tools—is critical for bridging the gap in advanced architectural skills.

#### B.4 MODEL PERFORMANCE BY MODALITY

In addition to the main set of frontier models, we conduct a comprehensive evaluation on 26 models spanning both small language models (SLMs) and large language models (LLMs), and breakdown performance by question modality. Results are summarized in Table B.4. This broader analysis highlights consistent trends across scale, including significant gaps in higher-order reasoning and

Figure 14: Topic-wise characterization of frontier models, categorized by skill. In order, the groupings of 3 radar plots correspond to "Recall", "Analyze", "Design", and "Implement" questions. Within each grouping, leftmost plot contains the best performing multimodal models, the middle plot contains the worst performing multimodal models, and the rightmost plot contains the two text-only models.

Table 4: Accuracy (%) of all evaluated models across the four skills in QUARCH. Best performing models in each category highlighted first, second, and third.

| Model                                |             | QuArch-Reasoning |             |             |         |  |

|--------------------------------------|-------------|------------------|-------------|-------------|---------|--|

|                                      | Recall      | Analyze          | Design      | Implement   | Overall |  |

| Closed-Source Multimodal Models      |             |                  |             |             |         |  |

| GPT-5                                | 89.0        | 72.1             | 86.7        | 71.0        | 72.4    |  |

| GPT-5 (Non-Reasoning)                | 86.3        | 49.5             | 52.4        | 40.7        | 49.0    |  |

| GPT-4o                               | 84.1        | 28.4             | 12.4        | 22.9        | 27.5    |  |

| Gemini 2.5 Pro                       | <b>87.4</b> | 63.3             | <b>59.0</b> | <b>59.7</b> | 62.9    |  |

| Gemini 2.5 Flash                     | 83.4        | 57.3             | <b>57.1</b> | 49.8        | 56.8    |  |

| Claude Sonnet 4                      | 85.5        | 49.0             | 36.2        | 46.8        | 48.4    |  |

| Claude 3.7 Sonnet Thinking           | 85.8        | 53.3             | 34.3        | 45.5        | 52.1    |  |

| Mistral Medium 3.1                   | 84.5        | 34.8             | 27.6        | 27.7        | 34.1    |  |

| Open-Source Multimodal Models        |             |                  |             |             |         |  |

| Gemma 3 27B IT                       | <b>75.6</b> | 22.4             | 15.2        | 16.0        | 21.7    |  |

| Gemma 3 4B IT                        | 62.3        | 7.6              | 2.9         | 3.5         | 7.2     |  |

| Llama 4 Maverick                     | 85.3        | 35.1             | 18.1        | 30.2        | 34.2    |  |

| Llama 3.2 11B                        | 69.4        | 8.8              | 1.0         | 4.0         | 8.2     |  |

| Mistral Small 3.2 24B Instruct       | <b>78.0</b> | 24.3             | 16.2        | 17.7        | 23.6    |  |

| Text-Only Models                     |             |                  |             |             |         |  |

| GPT-OSS 120B                         | 84.2        | 65.5             | 56.1        | <b>57.8</b> | 64.7    |  |

| DeepSeek R1                          | 86.9        | 57.4             | 38.6        | 47.1        | 56.1    |  |

| Llama 3.3 70B                        | 80.4        | 25.8             | 0.0         | 13.7        | 24.2    |  |

| Llama 3.2 1B                         | 36.5        | 1.7              | 0.0         | 1.0         | 1.6     |  |

| Mistral Codestral 2508               | 75.3        | 29.7             | 5.3         | 16.7        | 28.1    |  |

| Mistral Devstral Medium              | 81.9        | 29.0             | 3.5         | 22.5        | 27.7    |  |

| Kimi K2 0905                         | 84.2        | 43.9             | 35.1        | 37.3        | 43.2    |  |

| Qwen3 Coder 480B A35B Instruct       | 82.9        | 41.7             | 17.5        | 31.4        | 40.2    |  |

| Qwen3 235B A22B Thinking             | 85.6        | 62.2             | 50.9        | 52.9        | 61.3    |  |

| Qwen3 235B A22B NonThinking Instruct | 86.5        | 56.4             | 42.1        | 47.1        | 55.3    |  |

| Qwen3 Next 80B A3B Thinking          | 84.5        | 54.9             | 36.8        | 42.2        | 53.5    |  |

| Qwen3 30B A3B Thinking               | 82.5        | 50.0             | 31.6        | 37.3        | 48.6    |  |

| Qwen3 Coder 30B A3B Instruct         | 78.3        | 28.2             | 8.8         | 12.7        | 26.6    |  |

multimodal tasks compared to LLMs. By including this wider range of models, we provide a more complete picture of the landscape and enable future work to track progress not only at the frontier but also in more lightweight, cost-efficient models.

Table 6 provides detailed comparisons between text-only question performance, image-only performance, and image-text performance. See Sec 4 for interpretation and analysis of sensitivity to input modalities.

#### **B.5 PARTIALLY CORRECT JUDGMENTS**

Table 7 reports results when we extend the LLM-as-a-judge rubric to include a "Partially Correct" category. We observe that many models, particularly weaker or smaller ones, produce answers that are not fully correct but demonstrate partial understanding. For example, identifying the right concept while failing to complete all reasoning steps. Incorporating this intermediate category reveals a richer distribution of model behavior: some models that appear very weak under a strict correct/incorrect rubric (e.g., sub-30% accuracy) show substantially higher rates of partially correct answers, suggesting they are closer to reaching full correctness than raw accuracy alone would imply. At the same time, the strongest models still cluster most of their output into "Correct," with only modest use of the partially correct band. This analysis highlights that while partial correctness is less use-

Table 5: Per-generation accuracy (%) by evaluation type and modality. Best performing models in each category highlighted first, second, and third.

| Model                                | Text-only   |             | Image-only  | Image & Text |

|--------------------------------------|-------------|-------------|-------------|--------------|

|                                      |             | FRQ         | FRQ         | FRQ          |

| Closed-Source Multimodal Models      |             |             |             |              |

| GPT-5 (High Effort)                  | 89.0        | <b>74.7</b> | 70.5        | 72.7         |

| GPT-5                                | 86.4        | 53.8        | 44.8        | 49.4         |

| GPT-4o                               | 84.3        | 31.3        | 24.6        | 28.1         |

| Gemini 2.5 Pro                       | 87.5        | 63.9        | <b>62.1</b> | 63.0         |

| Gemini 2.5 Flash                     | 83.2        | 59.3        | 55.4        | 57.4         |

| Claude Sonnet 4                      | 85.6        | 52.1        | 45.4        | 48.8         |

| Claude 3.7 Sonnet Thinking           | 85.9        | 53.8        | 51.3        | 52.6         |

| Mistral Medium 3.1                   | 84.7        | 41.2        | 27.7        | 34.6         |

| Open-Source Multimodal Models        |             |             |             |              |

| Gemma 3 27B IT                       | 75.7        | 26.8        | 17.7        | 22.4         |

| Gemma 3 4B IT                        | 63.2        | 9.4         | 4.1         | 6.9          |

| Llama 4 Maverick                     | 85.9        | 36.1        | 32.1        | 34.2         |

| Llama 3.2 11B                        | 70.2        | 9.5         | 5.6         | 8.0          |

| Mistral Small 3.2 24B Instruct       | <b>78.6</b> | <b>29.1</b> | 17.7        | 23.5         |

| Text-Only Models                     |             |             |             |              |

| GPT-OSS 120B                         | 84.1        | 65.3        | -           | -            |

| DeepSeek R1                          | 87.1        | 56.2        | -           | -            |

| Llama 3.3 70B                        | 81.0        | 23.6        | -           | -            |

| Llama 3.2 1B                         | 37.1        | 0.8         | -           | -            |

| Mistral Codestral 2508               | 75.7        | 28.0        | -           | -            |

| Mistral Devstral Medium              | 82.5        | 27.3        | -           | -            |

| Kimi K2 0905                         | 84.2        | 44.2        | -           | -            |

| Qwen3 Coder 480B A35B Instruct       | 83.3        | 40.1        | -           | -            |

| Qwen3 235B A22B Thinking             | 85.6        | 61.7        | -           | -            |

| Qwen3 235B A22B NonThinking Instruct | 86.6        | 55.7        | -           | -            |

| Qwen3 Next 80B A3B Thinking          | 84.5        | 54.1        | -           | -            |

| Qwen3 30B A3B Thinking               | 82.7        | 48.8        | -           | -            |

| Qwen3 Coder 30B A3B Instruct         | 78.6        | 26.9        | -           | -            |

ful in practice for computer architecture tasks that often require precise answers, capturing it can provide a more diagnostic view of model progress and failure modes.

#### B.6 COMPARING HUMAN DOMAIN EXPERTS TO LLM-AS-A-JUDGE

We rigorously validate the fidelity of LLM judges used on QUARCH QAs compared to human expert evaluators in Sec. 4.4 and this section. We instruct LLM-as-a-Judge to reason about the accuracy of each freeform response with respect to the ground truth answer as though the response is from a student completing an academic exam (see prompts in Appendix D.3). The judge is instructed to grade each response as CORRECT, PARTIALLY-CORRECT, or INCORRECT. For our reported evaluations (Sec. 4.1), we recategorize each LLM-as-a-Judge assessment into a binary CORRECT or INCORRECT by rounding down PARTIALLY-CORRECT judge assessments to INCORRECT. The PARTIALLY-CORRECT category serves two purposes: it dis-incentivizes the judge from rounding up a nearly-correct answer to correct, and it enables analysis of fine-grained knowledge (Appendix B.5).

We generate multiple samples per question and multiple judgments per sample to control for model stochasticity, and report pass@k=1 across 3 samples (n=3) as defined in (Pinckney et al., 2025a). For each question in QUARCH, each model under evaluation (student s) generates 3 responses using the model's default generation parameters. For each individual student response, judge model j generates up to 3 assessments until a majority vote consensus is reached. For example, if on a given

Table 6: Per-generation accuracy (%) on the QUARCH benchmark broken down by evaluation type and modality. Best performing models in each category highlighted first, second, and third.

| Model                      | Text-only |             | Image-only | Image & Text |

|----------------------------|-----------|-------------|------------|--------------|

|                            | MCQ       | FRQ         | FRQ        | FRQ          |

| Multimodal Models          |           |             |            |              |

| GPT-5 (High Effort)        | 89.0      | 74.7        | 70.5       | 72.7         |

| GPT-5                      | 86.4      | 53.8        | 44.8       | 49.4         |

| Gemini 2.5 Pro             | 87.5      | 63.9        | 62.1       | 63.0         |

| Gemini 2.5 Flash           | 83.2      | <b>59.3</b> | 55.4       | 57.4         |

| Claude Sonnet 4            | 85.6      | 52.1        | 45.4       | 48.8         |

| Claude 3.7 Sonnet Thinking | 85.9      | 53.8        | 51.3       | 52.6         |

| Llama 4 Maverick           | 85.9      | 36.1        | 32.1       | 34.2         |

| Mistral Medium 3.1         | 84.7      | 41.2        | 27.7       | 34.6         |

| Text-Only Models           |           |             |            |              |

| GPT-OSS 120B               | 84.1      | 65.3        | -          | -            |

| DeepSeek R1                | 87.1      | 56.2        | -          | -            |

Table 7: Addition of "Partially Correct" Judgments in LLM-as-a-judge rubric. Results are pass@1 and using a single LLM-as-a-judge response rather than from consensus.

| Model                                 | Correct (%) | Partially Correct (%) | Incorrect (%) |

|---------------------------------------|-------------|-----------------------|---------------|

| Closed-Source Multimodal Models       |             |                       |               |

| GPT-5                                 | 70.4        | 19.2                  | 10.2          |

| GPT-5 (Non-Reasoning)                 | 48.5        | 31.6                  | 20.0          |

| GPT-40                                | 28.5        | 40.2                  | 31.3          |

| Gemini 2.5 Pro                        | 61.9        | 24.1                  | 13.8          |

| Gemini 2.5 Flash                      | 56.7        | 26.7                  | 16.5          |

| Claude Sonnet 4                       | 49.6        | 31.8                  | 18.6          |

| Claude 3.7 Sonnet Thinking            | 52.1        | 30.7                  | 16.9          |

| Mistral Medium 3.1                    | 33.5        | 34.5                  | 31.8          |

| Open-Source Multimodal Models         |             |                       |               |

| Gemma 3 27B Instruct                  | 24.0        | 35.2                  | 40.9          |

| Gemma 3 4B Instruct                   | 6.6         | 30.9                  | 62.5          |

| Llama 4 Maverick                      | 33.7        | 37.9                  | 28.5          |

| Llama 3.2 11B                         | 8.6         | 27.9                  | 63.5          |

| Mistral Small 3.2 24B Instruct        | 24.5        | 36.4                  | 39.0          |

| Text-Only Models                      |             |                       |               |

| GPT OSS 120B                          | 66.7        | 17.5                  | 15.8          |

| DeepSeek R1                           | 55.9        | 25.2                  | 18.8          |

| Llama 3.3 70B                         | 24.0        | 39.5                  | 36.2          |

| Llama 3.2 1B                          | 0.3         | 13.4                  | 86.3          |

| Mistral Codestral 2508                | 27.9        | 37.7                  | 33.9          |

| Mistral Devstral Medium               | 27.0        | 37.6                  | 35.2          |

| Kimi K2 0905                          | 45.4        | 25.8                  | 28.8          |

| Qwen 3 Coder 480B Instruct            | 40.7        | 34.8                  | 24.5          |

| Qwen 3 235B A22B Thinking             | 57.7        | 16.6                  | 25.6          |

| Qwen 3 235B A22B NonThinking Instruct | 54.4        | 26.5                  | 18.5          |

| Qwen 3 Next 80B Thinking              | 56.1        | 20.6                  | 23.2          |

| Qwen 3 30B A3B Thinking               | 48.0        | 21.7                  | 30.1          |

| Qwen 3 Coder 30B A3B Instruct         | 28.9        | 34.7                  | 36.2          |